#### UNIT I

#### **BOOLEAN ALGEBRA AND LOGIC GATES**

Number Systems - Arithmetic Operations - Binary Codes- Boolean Algebra and Logic Gates - Theorems and Properties of Boolean Algebra - Boolean Functions - Canonical and Standard Forms - Simplification of Boolean Functions using Karnaugh Map - Logic Gates – NAND and NOR Implementations.

#### Introduction

Basically there are two types of signals in electronics,

- i) Analog

- ii) Digital

#### Digital systems

#### Advantages:

- The usual advantages of digital circuits when compared to analog circuits are:Digital systems interface well with computers and are easy to control with software. New features can often be added to a digital system without changing hardware.

- Often this can be done outside of the factory by updating the product's software. So, the product's design errors can be corrected after the product is in a customer's hands.

- Information storage can be easier in digital systems than in analog ones. The noise-immunity of digital systems permits data to be stored and retrieved without degradation.

- ✤ In an analog system, noise from aging and wear degrade the information stored.

- In a digital system, as long as the total noise is below a certain level, the information can be recovered perfectly.

#### Disadvantages:

- In some cases, digital circuits use more energy than analog circuits to accomplish the same tasks, thus producing more heat as well. In portable or battery-powered systems this can limit use of digital systems.

- Digital circuits are sometimes more expensive, especially in small quantities. The sensed world is analog, and signals from this world are analog quantities.

- Digital circuits are sometimes more expensive, especially in small quantities. The sensed world is analog, and signals from this world are analog quantities.

- For example, light, temperature, sound, electrical conductivity, electric and magnetic fields are analog.

## **REVIEW OFNUMBER SYSTEMS**

Many number systems are in use in digital technology. The most common are the decimal, binary, octal, and hexadecimal systems. The decimal system is clearly the most familiar to us because it is tools that we use every day.

Types of Number Systems are

- Decimal Number system

- Binary Number system

- ✤ Octal Number system

- Hexadecimal Number system

| DECIMAL | BINARY | OCTAL | HEXADECIMAL |

|---------|--------|-------|-------------|

| 0       | 0000   | 0     | 0           |

| 1       | 0001   | 1     | 1           |

| 2       | 0010   | 2     | 2           |

| 3       | 0011   | 3     | 3           |

| 4       | 0100   | 4     | 4           |

| 5       | 0101   | 5     | 5           |

| 6       | 0110   | 6     | 6           |

| 7       | 0111   | 7     | 7           |

| 8       | 1000   | 10    | 8           |

| 9       | 1001   | 11    | 9           |

| 10      | 1010   | 12    | А           |

| 11      | 1011   | 13    | В           |

| 12      | 1100   | 14    | С           |

| 13      | 1101   | 15    | D           |

| 14      | 1110   | 16    | Е           |

| 15      | 1111   | 17    | F           |

## Table: Types of Number Systems

## Table: Numbersystemandtheir Base value

| Number Systems |      |                     |  |  |

|----------------|------|---------------------|--|--|

| System         | Base | Digits              |  |  |

| Binary         | 2    | 0 1                 |  |  |

| Octal          | 8    | 01234567            |  |  |

| Decimal        | 10   | 0 1 2 3 4 5 6 7 8 9 |  |  |

| Hexadecimal    | 16   | 0123456789ABCDEF    |  |  |

#### **Code Conversion:**

Convertingfromonecode formtoanothercode formiscalledcodeconversion, likeconvertingfrom binaryto decimal orconverting from hexadecimal to decimal.

### Binary-To-DecimalConversion:

Anybinarynumbercanbeconverted to its decimal equivalent simply by summing together the weights of the various positions in the binary number which contain a 1.

| Binary                           | Decimal          |

|----------------------------------|------------------|

| 110112                           |                  |

| $=2^{4}+2^{3}+0^{1}+2^{1}+2^{0}$ | =16+8+0+2+1      |

| Result                           | 27 <sub>10</sub> |

## Decimal to binary Conversion:

| Division | Remainder          | Binary                  |

|----------|--------------------|-------------------------|

| 25/2     | =12+remainder of1  | 1 (LeastSignificantBit) |

| 12/2     | =6 +remainder of0  | 0                       |

| 6/2      | =3 +remainder of0  | 0                       |

| 3/2      | =1 +remainder of l | 1                       |

| 1/2      | =0 +remainder of1  | 1 (MostSignificantBit)  |

| Result   | 25 <sub>10</sub>   | =11001 <sub>2</sub>     |

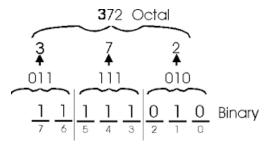

### Binary to octal:

Example: 100 111010<sub>2</sub>=(100)(111)(010)<sub>2</sub>=4 7 2<sub>8</sub>

### Octal to Binary:

### Decimal to octal:

| Division | Result            | Binary                   |

|----------|-------------------|--------------------------|

| 177/8    | =22+remainder of1 | 1 (LeastSignificantBit)  |

| 22/8     | =2 +remainder of6 | 6                        |

| 2 / 8    | =0 +remainder of2 | 2 (Most Significant Bit) |

| Result   | 177 <sub>10</sub> | =261 <sub>8</sub>        |

| Binary   |                   | =0101100012              |

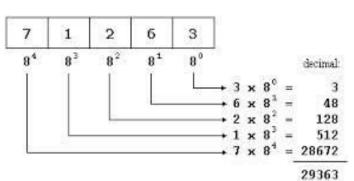

## Octal to Decimal: Example:

## Decimal to Hexadecimal:

| Division | Result             | Hexadecimal                 |

|----------|--------------------|-----------------------------|

| 378/16   | =23+remainder of10 | A(LeastSignificantBit)23    |

| 23/16    | =1 +remainder of7  | 7                           |

| 1/16     | =0 +remainder of1  | 1 (Most Significant Bit)    |

| Result   | 37810              | =17A <sub>16</sub>          |

| Binary   |                    | =00010111 1010 <sub>2</sub> |

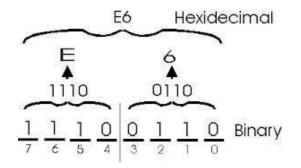

#### **Binary-To-Hexadecimal:**

Example:  $1011\ 0010\ 1111_2 = (1011)\ (0010)\ (1111)_2 = B2F_{16}$

#### Hexadecimal to binary:

### Octal-To-Hexadecimal / Hexadecimal-To-Octal Conversion:

- Convert Octal (Hexadecimal) to Binary first.

- \* Regroup the binary number by three bits per group starting from LSB if Octal is required.

- \* Regroup the binary number by four bits per group starting from LSB if Hexadecimal is required.

## Octal to Hexadecimal:

## (May 2014)

| Octal                           | Hexadecimal                             |

|---------------------------------|-----------------------------------------|

| =2 6 5 0                        |                                         |

| = <b>010</b> 110 <b>101</b> 000 | = <b>0101</b> 1010 <b>1000</b> (Binary) |

| Result                          | =(5A8) <sub>16</sub>                    |

Hexadecimal to octal:

| Hexadecimal         | Octal                                   |

|---------------------|-----------------------------------------|

| (5A8) <sub>16</sub> | = <b>0101</b> 1010 <b>1000</b> (Binary) |

|                     | = <b>010</b> 110 <b>101</b> 000(Binary) |

| Result              | =2 6 5 0(Octal)                         |

## 1's and2's complement:

- Complements are used in digital computers to simplify the subtraction operation and for logical manipulation.

- Thereare TWO types of complements for each base-rsystem: theradix complement and the diminished radix complement.

- The first is referred to as there's complement and the second as the (r-1)'scomplement, when the value of the baser is substituted in the name. The two types are referred to as the 2's complement and 1's complement for binary numbers and the 10's complement and 9's complement for decimal numbers.

## Note:

- The1's complement of a bin ary number is then umber that results when we change all 1 'sto zeros and the zeros to ones.

- The2's complement is the binary number that results whenweadd1 to the1's complement.

- It is used to represent negativenumbers.

### 2's complement=1'scomplement+1

**Example 1**) : Find 1's complement of  $(1101)_2$ 1 1 0 1 ← Number Sol:

$0010 \leftarrow 1$ 's complement

**Example 2)** : Find 2's complement of  $(1001)_2$ number

Sol: 1001

> $0110 \leftarrow 1$ 's complement + 1

0111

## **Diminished Radix Complement:**

Given a number N in base r having n digits, the (r-1)'s complement of N, i.e., its diminished radix complement, is defined as  $(r^n - 1) - N$ .

The9's complementof546700 is 999999-546700=453299.

The9's complementof012398 is 999999-012398= 987601.

### Radix Complement:

The r's complement of an n-digit number N in base r is defined as  $r^n - N$  for  $N \neq 0$  and as 0 for N = 0.

For examples: The10'scomplementof 012398 is 987602 The10'scomplementof246700 is 753300

#### Model 1:

Using10'scomplement, subtract72532-3250.

(Dec 2009)

|                           | M =   | 72532   |

|---------------------------|-------|---------|

| 10's complement o $fN =$  |       | +96750  |

|                           | Sum = | 169282  |

| Discard endcarry $10^5 =$ |       | -100000 |

| Answer =                  |       | 69282   |

## Model 2:

Using10'scomplement, subtract3250-72532.

M = 0325010s comp le mento fN = +<u>27468</u> Sum = 30718

### Model 3:

Given the two binary numbers X = 1010100 and Y = 1000011, perform the subtraction (a)X - Y and (b) Y - X by using 2's complements. [NOV – 2019]

(a) X = 1010100 2's complement of Y = + 0111101Sum = 10010001 Discard endcarry  $2^7 = -10000000$ Answer: X - Y = 0010001

(b)

*Y*= 1000011

2's complement of  $X = \underline{0101100}$

$$Sum = 1101111$$

There is no end carry. Therefore, the answer is Y- X=-(2's complementof1101111) = -0010001.

## Model 4:

Given the two binary numbers X=1010100 and Y= 1000011, perform the subtraction (a) X-Y and (b) Y-X by using 1's complements. (Dec 2009)

(a)X-Y=1010100-1000011

X = 10101001's complement of Y = +0111100Sum = 10010000 End around carry = +1

*Answer:***X**-**Y**= 0010001

**(b)** Y - X = 1000011 - 1010100

Y = 10000111's complement of X = +0101011Sum = 1101110

There is no end carry. Therefore, the answer is Y- X=-(1's complementof1101110)= -0010001.

## **ARITHMETIC OPERATIONS**

#### **Binary Addition:**

## **Rules of Binary Addition**

- 0+0=0

- 0 +1 =1

- 1 +0 =1

- 1 + 1 = 0, and carryl to the next most significant bit

Example:

#### Add: 00011010+00001100=00100110

|    |   | 1 | 1   |   |   |   |

|----|---|---|-----|---|---|---|

| 0  | 0 | 0 | 1 1 | 0 | 1 | 0 |

| +0 | 0 | 0 | 0 1 | 1 | 0 | 0 |

| 0  | 0 | 1 | 0 0 | 1 | 1 | 0 |

## **Binary Subtraction:**

## **Rules of Binary Subtraction**

•0 -0 =0

- •0 -1 =1, and borrow 1 from the next more significant bit

- •1 -0 =1

- •1 -1 =0

## Example:

| Sub: | 00100101-00010001=00010100 |   |   |   |   |   |   |   |

|------|----------------------------|---|---|---|---|---|---|---|

|      | 0                          | 0 | 1 | 0 | 0 | 1 | 0 | 1 |

|      | - 0                        | 0 | 0 | 1 | 0 | 0 | 0 | 1 |

|      | 0                          | 0 | 0 | 1 | 0 | 1 | 0 | 0 |

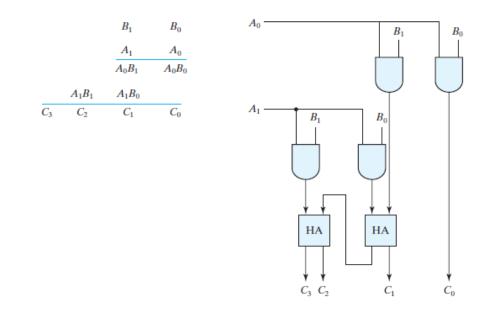

**Binary Multiplication:**

## ${\it Rules of Binary Multiplication}$

- 0 x 0 =0

- 0 x 1 =0

- 1 x 0 =0

- 1 x 1 =1,andnocarryorborrowbits

## **Example:**Multiply the following binary numbers:

(a) 0111 and 1101

(b) 1.011 and 10.01.

| (a) $0111 \times 1101$ |  |

|------------------------|--|

|------------------------|--|

|   |   |   | 0   | 1 | 1 | 1 | Multiplicand         |

|---|---|---|-----|---|---|---|----------------------|

|   |   |   | × 1 | 1 | 0 | 1 | Multiplier           |

|   |   |   | 0   | 1 | 1 | 1 |                      |

|   |   | 0 | 0   | 0 | 0 |   | Partial              |

|   | 0 | 1 | 1   | 1 |   |   | Products             |

| 0 | 1 | 1 | 1   |   |   |   |                      |

| 1 | 0 | 1 | 1   | 0 | 1 | 1 | <b>Final Product</b> |

### (b) $1.011 \times 10.01$

|   |    |   | 1.         | 0  | 1 | 1 | Multiplicand  |

|---|----|---|------------|----|---|---|---------------|

|   |    |   | $\times 1$ | 0. | 0 | 1 | Multiplier    |

|   |    |   | 1          | 0  | 1 | 1 | )             |

|   |    | 0 | 0          | 0  | 0 |   | Partial       |

|   | 0  | 0 | 0          | 0  |   |   | Products      |

| 1 | 0  | 1 | 1          |    |   |   | )             |

| 1 | 1. | 0 | 0          | 0  | 1 | 1 | Final Product |

## **Binary Division:**

Binarydivisionisthe repeatedprocess of subtraction, just as indecimal division. **Example: Divide the following**

| (a)        | 11001 ÷      | 101  |   |   |   |    |   |   |   |   |

|------------|--------------|------|---|---|---|----|---|---|---|---|

|            |              |      |   | 1 | 0 | 1  |   |   |   |   |

|            | 1            | 0    | 1 | 1 | 1 | 0  | 0 | 1 |   |   |

|            |              |      |   | 1 | 0 | 1  |   |   |   |   |

|            |              |      |   | 0 | 0 | 1  | 0 | 1 |   |   |

|            |              |      |   |   |   | 1  | 0 | 1 |   |   |

|            |              |      |   |   |   | 0  | 0 | 0 | - |   |

| <i>(b)</i> | 11110 $\div$ | 1001 |   |   |   |    |   |   |   |   |

|            |              |      |   |   | 1 | 1. | 0 | 1 | 0 |   |

| 1          | 0            | 0    | 1 | 1 | 1 | 1  | 1 | 0 |   |   |

|            |              |      |   |   | 1 | 0  | 0 | 1 |   |   |

|            |              |      |   | 0 | 1 | 1  | 0 | 0 |   |   |

|            |              |      |   |   | 1 | 0  | 0 | 1 |   |   |

|            |              |      |   |   | 1 | 0  | 0 | 0 |   | 0 |

|            |              |      |   |   |   | 1  | 0 | 0 |   | 1 |

|            |              |      |   |   |   |    | 1 | 1 |   | 0 |

|            |              |      |   |   |   | 1  | 0 | 0 |   | 1 |

|            |              |      |   |   |   |    | 1 | 0 |   | 1 |

\*\*\*\*\*\*

## BINARYCODES

# Explain the various codes used in digital systems with an example.(or)Explain in detail about Binary codes with an example

- > In digital systems a variety of codes are used to serve different purposes, such as data entry, arithmetic operation, error detection and correction, etc.

- > Selection of a particular codedepends on the requirement.

- > Binarycodesarecodeswhicharerepresented in binary system with modification from the original ones.

- Codes can be broadly classified into five groups.

- (i) Weighted Binary Codes

- (ii) Non-weighted Codes

- (iii) Error-detection Codes

- (iv) Error-correcting Codes

- (v) Alphanumeric Codes

## Weighted Binary Codes

If each position of a number represents a specific weight then the coding scheme is called weighted binary code.

## BCD Code or 8421 Code:

The full form of BCD is 'Binary-Coded Decimal'. Since this is a coding scheme relating decimal and binary numbers, *four bits are required* to code each decimal number.

- A decimal number in BCD (8421) is the same as its equivalent binary number only when the number is between 0 and 9. A BCD number greater than 10 looks different from its equivalent binary number, even though both contain 1's and 0's. Moreover, the binary combinations 1010 through 1111 are not used and have no meaning in BCD.

- Consider decimal 185 and its corresponding value in BCD and binary:

$(185)_{10} = (0001 \ 1000 \ 0101)_{BCD} = (10111001)_2$

- For example,  $(35)_{10}$  is represented as 0011 0101 using BCD code, rather than  $(100011)_2$

- *Example: Give the BCD equivalent for the decimal number 589.*

| The decimal number is                      | 5   | 8      | 9    |  |  |

|--------------------------------------------|-----|--------|------|--|--|

| BCD code is                                | 010 | 1 1000 | 1001 |  |  |

| Hence, $(589)_{10} = (010110001001)_{BCD}$ |     |        |      |  |  |

### 2421 Code:

- Another weighted code is 2421 code. The weights assigned to the four digits are 2, 4,2, and 1.

- > The 2421 code is the same as that in BCD from 0 to 4. However, it varies from 5 to 9.

- > For example, in this case the bit combination 0100 represents decimal 4; whereas the bit combination 1101 is interpreted as the decimal 7, as obtained from  $2 \times 1 + 1 \times 4 + 0 \times 2 + 1 \times 1 = 7$ .

- > This is also a self-complementary code.

## BCD Addition:

Examples:

• Consider the addition of 184 + 576 = 760 in BCD:

| BCD        | 1     | 1     |      |      |

|------------|-------|-------|------|------|

|            | 0001  | 1000  | 0100 | 184  |

|            | +0101 | 0111  | 0110 | +576 |

| Binary sum | 0111  | 10000 | 1010 |      |

| Add 6      |       | 0110  | 0110 |      |

| BCD sum    | 0111  | 0110  | 0000 | 760  |

Add the following BCD numbers: (a) 1001 and 0100, (b) 00011001 and 00010100

| Solution  |                                                      |            |

|-----------|------------------------------------------------------|------------|

| (a)       | 1001                                                 |            |

|           | $\div 0 1 0 0$                                       |            |

|           | $1  1  0  1 \rightarrow \text{Invalid BCD number}$   | <b>(</b> ) |

|           | $+0$ 1 1 0 $\rightarrow$ Add 6                       | ··-1       |

| 0 0 0     | $1  0  0  1  1 \rightarrow \text{Valid BCD number}$  | 13         |

| 1         | 3                                                    | 1          |

| (b) 0 0 0 | 1 1 0 0 1                                            | . '        |

| +0 0 0    | 1 0 1 0 0                                            |            |

| 0 0 1     | $0$ 1 1 0 1 $\rightarrow$ Right group is invalid     | 19         |

|           | $+0$     $0 \rightarrow \text{Add} 6$                |            |

| 0 0 1     | $1  0  0  1  1  \rightarrow \text{Valid BCD number}$ | 33.        |

| 3         |                                                      |            |

| Decimal<br>Digit | BCD<br>8421 | 2421 | Excess-3 | 8, 4, -2, -1 |

|------------------|-------------|------|----------|--------------|

| 0                | 0000        | 0000 | 0011     | 0000         |

| 1                | 0001        | 0001 | 0100     | 0111         |

| 2                | 0010        | 0010 | 0101     | 0110         |

| 3                | 0011        | 0011 | 0110     | 0101         |

| 4                | 0100        | 0100 | 0111     | 0100         |

| 5                | 0101        | 1011 | 1000     | 1011         |

| 6                | 0110        | 1100 | 1001     | 1010         |

| 7                | 0111        | 1101 | 1010     | 1001         |

| 8                | 1000        | 1110 | 1011     | 1000         |

| 9                | 1001        | 1111 | 1100     | 1111         |

|                  | 1010        | 0101 | 0000     | 0001         |

| Unused           | 1011        | 0110 | 0001     | 0010         |

| bit              | 1100        | 0111 | 0010     | 0011         |

| combi-           | 1101        | 1000 | 1101     | 1100         |

| nations          | 1110        | 1001 | 1110     | 1101         |

|                  | 1111        | 1010 | 1111     | 1110         |

## Four Different Binary Codes for the Decimal Digits

### Non-weighted Codes

- ▶ It basically means that each position of the binary number is not assigned a fixed value.

- Excess-3 codes and Gray codes are such non-weighted codes.

### Excess-3 code:

Excess-3 is a non-weighted code used to express decimal numbers. The code derives its name from the fact that each binary code is the corresponding 8421 code plus 0011(3).

Example:1000of8421 (BCD)=1011 in Excess-3

$\diamond$  Convert (367)<sub>10</sub> into its Excess-3 code. Solution. The decimal number is 3 6 7Add 3 to each bit +3 +3 +3 6 9 Sum 10Converting the above sum into 4-bit binary equivalent, we have a 4-bit binary equivalent of 0110 1001 1010 Hence, the Excess-3 code for  $(367)_{10} = 0110 \ 1001 \ 1010$

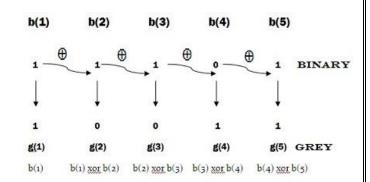

## Graycode:

- The graycode belongs to aclass of code scalled minimum change codes, in which only one bit in the code changes when moving from one code to the next.

- TheGraycodeisnon-weightedcode, as the position of bit does not contain any weight. In digital Graycode has got a special place.

| Decimal<br>Number | BinaryCode | Gray Code |

|-------------------|------------|-----------|

| 0                 | 0000       | 0000      |

| 1                 | 0001       | 0001      |

| 2                 | 0010       | 0011      |

| 3                 | 0011       | 0010      |

| 4                 | 0100       | 0110      |

| 5                 | 0101       | 0111      |

| 6                 | 0110       | 0101      |

| 7                 | 0111       | 0100      |

| 8                 | 1000       | 1100      |

| 9                 | 1001       | 1101      |

| 10                | 1010       | 1111      |

| 11                | 1011       | 1110      |

| 12                | 1100       | 1010      |

| 13                | 1101       | 1011      |

| 14                | 1110       | 1001      |

| 15                | 1111       | 1000      |

- The graycode is a reflective digital code which has the special property that any two subsequent numbers codes differ by only one bit. This is also called a *unit-distance code*.

- Important when an analog quantity must be converted to a digital representation. Only one bitch anges between two successive integers which are being coded.

## Example:

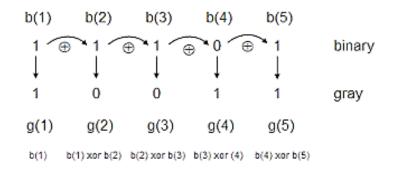

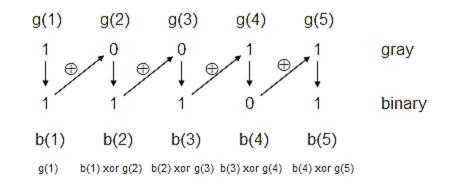

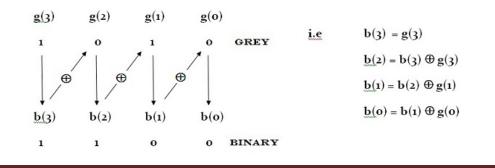

## Binary toGray CodeConversion:

Any binary number can be converted into equivalent Gray code by the following steps:

- i) the MSB of the Gray code is the same as the MSB of the binary number;

- ii) the second bit next to the MSB of the Gray code equals the Ex-OR of the MSB and second bit of the binary number; it will be 0 if there are same binary bits or it will be 1 for different binary bits;

- iii) the third bit for Gray code equals the exclusive-OR of the second and third bits of the binary number, and similarly all the next lower order bits follow the same mechanism.

## GrayCode to Binary Code Conversion:

Any Gray code can be converted into an equivalent binary number by the following steps:

- i. The MSB of the binary number is the same as the MSB of the Gray code.

- ii. the second bit next to the MSB of the binary number equals the Ex-OR of the MSB of the binary number and second bit of the Gray code; it will be 0 if there are samebinary bits or it will be 1 for different binary bits;

- iii. the third bit for the binary number equals the exclusive-OR of the second bit of the binary number and third bit of the Gray code, and similarly all the next lower orderbits follow the same mechanism.

#### Errordetectingcodes

- Whendataistransmitted from one point to another, like inwire less transmission, like inhard disk sand memories, there are chances that data may get corrupted.

- ➤ Todetectthesedata errors, we use special codes, which are error detection codes.

#### Twotypes ofparity

- Evenparity:Checksifthereisanevennumberofones;ifso,paritybitiszero.Whenthenumberof one'sisoddthenparitybitissetto 1.

- OddParity:Checksifthereisanoddnumberofones;ifso,paritybitiszero.

Whenthenumberof one'siseventhenparitybitis set to 1.

#### Errorcorrectingcode

- Error-correctingcodes not only detecter rors, but also correct them.

- > This is used normally in Satellite communication, where turn-around delay is very high as is the

B.ARUNKUMAR, Asst. Prof.,/ECE

or it is just stored,

probabilityofdata gettingcorrupt.

## Hamming codes

- Hammingcodeaddsaminimumnumberofbitstothedatatransmitted correct everypossible one-bit error.

- It candetect(not correct)two-biterrorsandcannotdistinguish between1-bitand2-bits inconsistencies. Itcan't-ingeneral-detect 3(ormore)-bits errors.

## Alphanumeric Codes

An alphanumeric code is a binary code of a group of elements consisting of ten decimal digits, the 26 letters of the alphabet (both in uppercase and lowercase), and a certain number of special symbols such as #, /, &, %, etc.

## ASCII(AmericanStandardCode for InformationInterchange)

- $\succ$  It is actually a 7-bit code, where a character is represented with seven bits.

- > The character is stored as one byte with one bit remainingunused.

- ▶ But often the extra bit is used to extend the ASCII to represent an additional128 characters.

## EBCDIC codes

- > EBCDICstandsforExtendedBinary CodedDecimalInterchange.

- It is also an alphanumeric code generally used in IBM equipment and in large computers for communicating alphanumeric data.

- For the different alphanumeric characters the code grouping in this code is different from the ASCII code. It is actually an 8-bit code and a ninth bit is added as the parity bit.

## Boolean Algebra and Theorems

## Explain various theorems of Boolean algebra. (Nov – 2018) Definition:

Boolean algebra is an algebraic structure defined by a set of elements B, together with two binary operators. '+' and '-', provided that the following (Huntington) postulates are satisfied;

## Theorems of Boolean algebra:

The theorems of Boolean algebra can be used to simplify many a complex Boolean expression and also to transform the given expression into a more useful and meaningful equivalent expression.

## T1: Commutative Law

(a) A + B = B + A

(b) A B = B A

## T2: Associative Law

(a) (A + B) + C = A + (B + C)

(b) (A B) C = A (B C)

## T3: Distributive Law

(a) A (B + C) = A B + A C(b) A + (B C) = (A + B) (A + C)

## T4: Identity Law

(a) A + A = A(b) A A = A

## T5: Negation Law

$(\overline{A}) = \overline{A}$  and  $(\overline{A}) = A$

## Postulates of Boolean algebra:

The postulates of a mathematical system form the basic assumptions from which it possible to deduce the rules, theorems, and properties of the system. The following are the important postulates of Boolean algebra:

1.1.1 = 1,0+0 = 0.

- 2. 1.0 = 0.1 = 0, 0+1 = 1+0 = 1.

- 3. 0.0 = 0, 1+1 = 1

4. 1' = 0 and 0' = 1.

Many theorems of Boolean algebra are based on these postulates, which can be used to simplifyBoolean expressions.

The operators and postulates have the following meanings:

- $\checkmark$  The binary operator + defines addition.

- $\checkmark$  The additive identity is 0.

- $\checkmark$  The additive inverse defines subtraction.

- ✓ The binary operator .(dot) defines multiplication.

- $\checkmark$  The multiplicative identity is 1.

- ✓ The only distributive law applicable is that of .(dot) over +:

## T6: Redundancy

| (a) | A + A B = A |

|-----|-------------|

| (b) | A(A+B) = A  |

## T7: Operations with '0' & '1'

- (a) 0 + A = A

- (b) IA = A

- (c) 1 + A = 1(d) 0A = 0

- T8 : Complement laws

- (a)  $\overline{A} + A = 1$

(b)

$$\bar{A} \cdot A = 0$$

**T9:** (a)  $A + \overline{AB} = A + B$ (b) A.  $(\overline{A} + B) = A.B$   $a \cdot (b + c) = (a \cdot b) + (a \cdot c)$

## **Two-Valued Boolean Algebra:**

A two-valued Boolean algebra is defined on a set of two elements,  $B = \{0, 1\}$ , with rules for the two binary operators + and .(dot) as shown in the following operator tables.

| x | y | x·y | x | y | x + y | x | <b>x</b> ′ |

|---|---|-----|---|---|-------|---|------------|

| 0 | 0 | 0   | 0 | 0 | 0     | 0 | 1          |

| 0 | 1 | 0   | 0 | 1 | 1     | 1 | 0          |

| 1 | 0 | 0   | 1 | 0 | 1     |   |            |

| 1 | 1 | 1   | 1 | 1 | 1     |   |            |

## **Duality Principle:**

The *duality principle* states that every algebraic expression deducible from the postulates of Boolean algebra remains valid if the operators and identity elements are interchanged. If the dual of an algebraic expression is desired, we simply interchange OR and AND operators and replace 1's by 0's and 0's by 1's.

## **DeMorgan's theorem:**

- 1. The complement of product is equal to the sum of their complements. (X,Y)'=X'+Y'

- 2. The complement of sum is equal to the product of their complements. (X+Y)' = X'.Y'

## **Basic Theorems:**

| Postulates and Theorems o | f Bool | ean Algebra               |     |                         |

|---------------------------|--------|---------------------------|-----|-------------------------|

| Postulate 2               | (a)    | x + 0 = x                 | (b) | $x \cdot 1 = x$         |

| Postulate 5               | (a)    | x + x' = 1                | (b) | $x \cdot x' = 0$        |

| Theorem 1                 | (a)    | x + x = x                 | (b) | $x \cdot x = x$         |

| Theorem 2                 | (a)    | x + 1 = 1                 | (b) | $x \cdot 0 = 0$         |

| Theorem 3, involution     |        | (x')' = x                 |     |                         |

| Postulate 3, commutative  | (a)    | x + y = y + x             | (b) | xy = yx                 |

| Theorem 4, associative    | (a)    | x + (y + z) = (x + y) + z | (b) | x(yz) = (xy)z           |

| Postulate 4, distributive | (a)    | x(y+z) = xy + xz          | (b) | x + yz = (x + y)(x + z) |

| Theorem 5, DeMorgan       | (a)    | (x + y)' = x'y'           | (b) | (xy)' = x' + y'         |

| Theorem 6, absorption     | (a)    | x + xy = x                | (b) | x(x + y) = x            |

State and prove postulates and theorems of Boolean algebra.

)

#### **THEOREM 1(a):** x + x = x.

| Statement                 | Justification  |

|---------------------------|----------------|

| $x + x = (x + x) \cdot 1$ | postulate 2(b) |

| = (x+x)(x+x')             | 5(a)           |

| = x + xx'                 | 4(b)           |

| = x + 0                   | 5(b)           |

| = x                       | 2(a)           |

**THEOREM 1(b):**  $x \cdot x = x$ .

| Statement            | Justification  |

|----------------------|----------------|

| $x \cdot x = xx + 0$ | postulate 2(a) |

| = xx + xx'           | 5(b)           |

| = x(x + x')          | 4(a)           |

| $= x \cdot 1$        | 5(a)           |

| = x                  | 2(b)           |

**THEOREM 2(a):** x + 1 = 1.

| Statement                 | Justification  |

|---------------------------|----------------|

| $x + 1 = 1 \cdot (x + 1)$ | postulate 2(b) |

| = (x + x')(x + 1)         | 5(a)           |

| $= x + x' \cdot 1$        | 4(b)           |

| = x + x'                  | 2(b)           |

| = 1                       | 5(a)           |

**THEOREM 2(b):**  $x \cdot 0 = 0$  by duality.

**THEOREM 3:** (x')' = x. From postulate 5, we have x + x' = 1 and  $x \cdot x' = 0$ , which together define the complement of x. The complement of x' is x and is also (x')'.

**THEOREM 6(a):** x + xy = x.

| Statement                 | Justification  |  |  |  |  |

|---------------------------|----------------|--|--|--|--|

| $x + xy = x \cdot 1 + xy$ | postulate 2(b) |  |  |  |  |

| =x(1+y)                   | 4(a)           |  |  |  |  |

| = x(y + 1)                | 3(a)           |  |  |  |  |

| $= x \cdot 1$             | 2(a)           |  |  |  |  |

| = x                       | 2(b)           |  |  |  |  |

**THEOREM 6(b):** x(x + y) = x by duality.

\*\*\*\*\*\*

#### **Boolean Functions**

- Boolean algebra is an algebra that deals with binary variables and logic operations. A Boolean function described by an algebraic expression consists of binary variables, the constants 0 and 1, and the logic operation symbols.

- For a given value of the binary variables, the function can be equal to either 1 or 0.

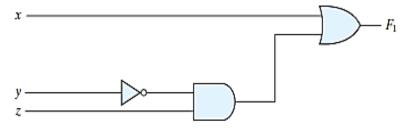

#### **Example**, consider the Boolean functionF1 = x + y'z

The function F1 is equal to 1 if x is equal to 1 or if both y' and z are equal to 1. F1 is equal to 0 otherwise. The complement operation dictates that when y' = 1, y = 0. Therefore, F1 = 1 if x = 1 or if y = 0 and z = 1. A Boolean function expresses the logical relationshipbetween binary variables and is evaluated by determining the binary value of the expression for all possible values of the variables. The gate implementation of F1 is shown below.

#### **Example: Consensus Law: (function 4)**

Simplify the following Boolean functions to a minimum number of literals.

1.

$$x(x' + y) = xx' + xy = 0 + xy = xy$$

.

2.  $x + x'y = (x + x')(x + y) = 1(x + y) = x + y$ .

3.  $(x + y)(x + y') = x + xy + xy' + yy' = x(1 + y + y') = x$ .

4.  $xy + x'z + yz = xy + x'z + yz(x + x')$

$= xy + x'z + xyz + x'yz$

$= xy(1 + z) + x'z(1 + y)$

$= xy + x'z$ .

5.  $(x + y)(x' + z)(y + z) = (x + y)(x' + z)$ , by duality from function 4.

## Complement of a function:

The complement of a function F is obtained from an interchange of 0's for 1's and 1's for 0's in the value of F.

Example: 1.

$(A + B + C)' = (A + x)' \qquad \text{let } B + C = x$ = A'x' by theorem 5(a) (DeMorgan) = A'(B + C)' substitute B + C = x = A'(B'C') by theorem 5(a) (DeMorgan) = A'B'C' by theorem 4(b) (associative) 2. Find the complement of the functions  $F1 = x^2yz^2 + x^2y^2z$  and  $F2 = x(y^2z^2 + yz)$ . By applying DeMorgan's theorems as many times as necessary, the complements are obtained as follows:

$$F'_{1} = (x'yz' + x'y'z)' = (x'yz')'(x'y'z)' = (x + y' + z)(x + y + z')$$

$$F'_{2} = [x(y'z' + yz)]' = x' + (y'z' + yz)' = x' + (y'z')'(yz)'$$

$$= x' + (y + z)(y' + z')$$

$$= x' + yz' + y'z$$

3. Find the complement of the functions F1 = x'yz' + x'y'z and F2 = x(y'z' + yz) by taking their duals and complementing each literals.

Solution:

- 1.  $F_1 = x'yz' + x'y'z$ . The dual of  $F_1$  is (x' + y + z')(x' + y' + z). Complement each literal:  $(x + y' + z)(x + y + z') = F'_1$ .

- 2.  $F_2 = x(y'z' + yz)$ . The dual of  $F_2$  is x + (y' + z')(y + z). Complement each literal:  $x' + (y + z)(y' + z') = F'_2$ .

## Canonical and Standard forms:

Explain canonical SOP & POS form with suitable example.

> Binary logic values obtained by the logical functions and logic variables are in binary form. An arbitrary logic function can be expressed in the following forms.

(i) Sum of the Products (SOP)

- (ii) Product of the Sums (POS)

- > Boolean functions expressed as a sum of minterms or product of maxterms are said to be in canonical form.

## Product term:

The AND function is referred to as a product. The variable in a product term can appear either in complementary or uncomplimentary form. Example: ABC'

## Sum term:

The OR function is referred to as a Sum. The variable in a sum term can appear either in complementary or uncomplimentary form. Example: A+B+C'

## **Sum of Product (SOP):**

The logical sum of two or more logical product terms is called sum of product expression. It is basically an OR operation of AND operated variables. **Example: Y=AB+BC+CA**

## **Product of Sum (POS):**

The logical product of two or more logical sum terms is called product of sum expression. It is basically an AND operation of OR operated variables. Example: Y=(A+B).(B+C).(C+A)

#### Minterm:

A product term containing all the K variables of the function in either complementary or uncomplimentary form is called Minterm or standard product.

## Maxterm:

A sum term containing all the K variables of the function in either complementary or uncomplementary form is called Maxterm or standard sum.

|   |   |   | Minterms |                       | Maxte        | erms        |

|---|---|---|----------|-----------------------|--------------|-------------|

| x | y | z | Term     | Designation           | Term         | Designation |

| 0 | 0 | 0 | x'y'z'   | $m_0$                 | x + y + z    | $M_0$       |

| 0 | 0 | 1 | x'y'z    | $m_1$                 | x + y + z'   | $M_1$       |

| 0 | 1 | 0 | x'yz'    | $m_2$                 | x + y' + z   | $M_2$       |

| 0 | 1 | 1 | x'yz     | $m_3$                 | x + y' + z'  | $M_3$       |

| 1 | 0 | 0 | xy'z'    | $m_4$                 | x' + y + z   | $M_4$       |

| 1 | 0 | 1 | xy'z     | <i>m</i> <sub>5</sub> | x' + y + z'  | $M_5$       |

| 1 | 1 | 0 | xyz'     | $m_6$                 | x' + y' + z  | $M_6$       |

| 1 | 1 | 1 | xyz      | $m_7$                 | x' + y' + z' | $M_7$       |

Minterms and Maxterms for Three Binary Variables

### Canonical SOP Expression:

The minterms whosesum defines the Boolean function are those which give the 1's of the function in a truth table.

## Procedure for obtaining Canonical SOP expression:

- ✓ Examine each term in a given logic function. Retain if it is a minterm, continue to examine the next term in the same manner.

- ✓ Check for the variables that are missing in each product which is not minterm. Multiply the product by  $(X+X^2)$ , for each variable X that is missing.

- $\checkmark$  Multiply all the products and omit the redundant terms.

## Example:

*Express the Boolean function* F = A + BC *as a sum of minterms.* (*May -10*)(*Nov - 2018*) Solution:

The function has three variables: *A*, *B*, and *C*.

The first term A is missing two variables; therefore,

A = A(B + B') = AB + AB'

This function is still missing one variable, so

A = AB(C + C') + AB'(C + C')

=ABC + ABC' + AB'C + AB'C'

The second term B'C is missing one variable; hence,

$B^{\prime}C = B^{\prime}C(A + A^{\prime}) = AB^{\prime}C + A^{\prime}B^{\prime}C$

Combining all terms, we have

$F = A + B^{\circ}C = ABC + ABC^{\circ} + AB^{\circ}C + AB^{\circ}C^{\circ} + A^{\circ}B^{\circ}C$

But  $AB^{*}C$  appears twice, and according to theorem 1 (x + x = x), it is possible toremove one of those occurrences. Rearranging the minterms in ascending order, we finally obtain

F = A'B'C + AB'C' + AB'C + ABC' + ABC = m1 + m4 + m5 + m6 + m7F(A, B, C) =  $\sum (1, 4, 5, 6, 7)$

## Example: Obtain the canonical sum of product form of the following function. (May 2014)

F (A, B, C) = A + BC = A (B + B') (C + C') + BC (A + A') = (AB + AB') (C + C') + ABC + A'BC = ABC + AB'C + ABC' + AB'C' + ABC + A'BC = ABC + AB'C + ABC' + AB'C' + A'BC (as ABC + ABC = ABC)

Hence the canonical sum of the product expression of the given function is

F(A, B) = ABC + AB'C + ABC' + AB'C' + A'BC.

#### **Canonical POS Expression:**

The Maxterms whose product defines the Boolean function are those which give the 1's of the function in a truth table.

## Procedure for obtaining Canonical POS expression:

- ✓ Examine each term in a given logic function. Retain if it is a maxterm, continue to examine the next term in the same manner.

- ✓ Check for the variables that are missing in each sum which is not maxterm. Add (X.X'), for each variable X that is missing.

- $\checkmark$  Expand the expression using distributive property eliminate the redundant terms.

#### Example:

Express the Boolean function F = xy + x'z as a product of maxterms. First, convert the function into OR terms by using the distributive law:

$$F = xy + x'z = (xy + x')(xy + z) = (x + x')(y + x')(x + z)(y + z) = (x' + y)(x + z)(y + z)$$

The function has three variables: x, y, and z. Each OR term is missing one variable; therefore,

$$x' + y = x' + y + zz' = (x' + y + z)(x' + y + z')$$

$$x + z = x + z + yy' = (x + y + z)(x + y' + z)$$

$$y + z = y + z + xx' = (x + y + z)(x' + y + z)$$

Combining all the terms and removing those which appear more than once, we finally obtain

$$F = (x + y + z)(x + y' + z)(x' + y + z)(x' + y + z')$$

=  $M_0 M_2 M_4 M_5$

A convenient way to express this function is as follows:

$$F(x, y, z) = \Pi(0, 2, 4, 5)$$

#### Example:

#### Obtain the canonical product of the sum form of the following function.

F(A, B, C) = (A + B')(B + C)(A + C')

(Dec 2012)

Solution:

$\begin{array}{l} F\ (A,\ B,\ C) = (A + B')\ (B + C)\ (A + C') \\ = (A + B' + 0)\ (B + C + 0)\ (A + C' + 0) \\ = (A + B' + CC')\ (B + C + AA')\ (A + C' + BB') \\ = (A + B' + C)\ (A + B' + C')\ (A + B + C)\ (A' + B + C)\ (A + B + C') \\ (A + B' + C') \\ [using the distributive property, as X + YZ = (X + Y)(X + Z)] \\ = (A + B' + C)\ (A + B' + C')\ (A + B + C)\ (A' + B + C)\ (A + B + C') \\ [as\ (A + B' + C')\ (A + B' + C') = A + B' + C'] \end{array}$ Hence the canonical product of the sum expression for the given function is

F (A, B, C) = (A + B' + C) (A + B' + C') (A + B + C) (A' + B + C) (A + B + C')

\*\*\*\*\*

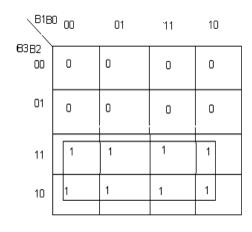

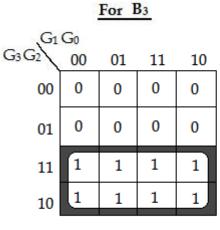

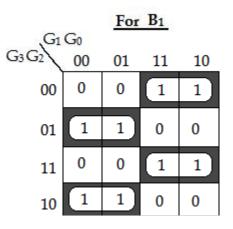

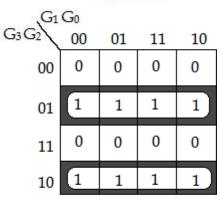

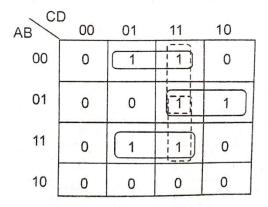

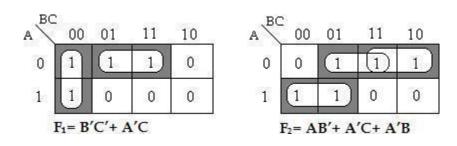

#### Karnaugh Map (K-map):

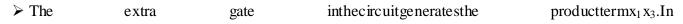

- Using Boolean algebra to simplify Boolean expressions can be difficult. The Karnaugh map provides a simple and straight-forward method of minimizing Boolean expressions which represent combinational logic circuits.

- A Karnaugh map is a pictorial method of grouping together expressions with common factors and then eliminating unwanted variables.

- ✤ A Karnaugh map is a two-dimensional truth-table. Note that the squares are numbered so that the binary representations for the numbers of two adjacent squares differ in exactly one position.

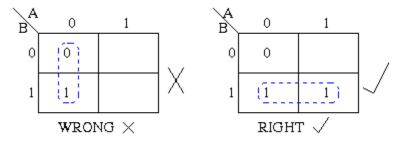

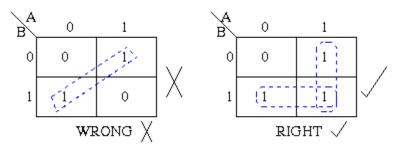

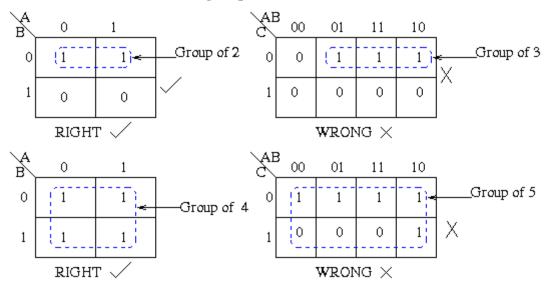

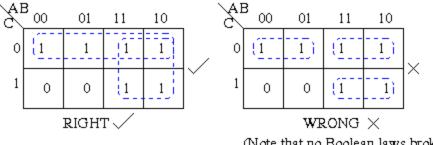

### Rules for Grouping together adjacent cells containing 1's:

- Groups must contain 1, 2, 4, 8, 16  $(2^n)$  cells.

- Groups must contain only 1 (and X if don't care is allowed).

- Groups may be horizontal or vertical, but not diagonal.

- Groups should be as large as possible.

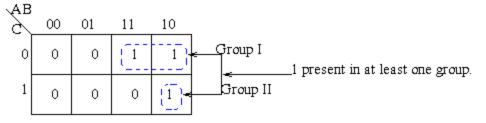

- Each cell containing a 1 must be in at least one group.

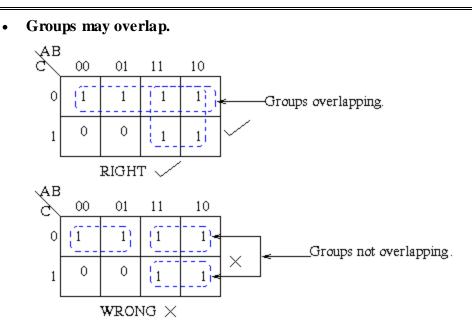

- Groups may overlap.

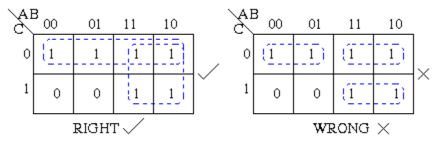

- Groups may wrap around the table. The leftmost cell in a row may be grouped with the rightmost cell and the top cell in a column may be grouped with the bottom cell.

- There should be as few groups as possible.

### **Obtaining Product Terms**

- If A is a variable that has value 0 in all of the squares in the grouping, then the complemented form A is in the product term.

- If A is a variable that has value 1 in all of the squares in the grouping, then the true form A is in the product term.

• If A is a variable that has value 0 for some squares in the grouping and value 1 for others, then it is not in the product term

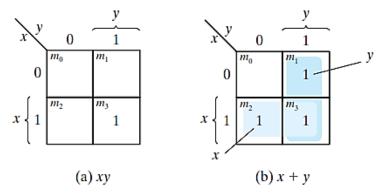

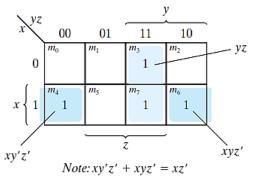

## The Format of K-Maps:

## K-Maps of 2 Variables:

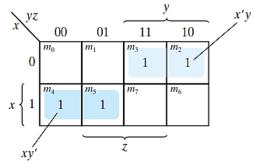

## K-Maps of 3 Variables:

Simplify the boolean function

$F(x, y, z) = \sum (2, 3, 4, 5)$

$F(x, y, z) = \Sigma(2, 3, 4, 5) = x'y + xy'$

$F(x, y, z) = \sum 3, 4, 6, 7$

Simplify the boolean function

$F(x, y, z) = \Sigma(3, 4, 6, 7) = yz + xz'$

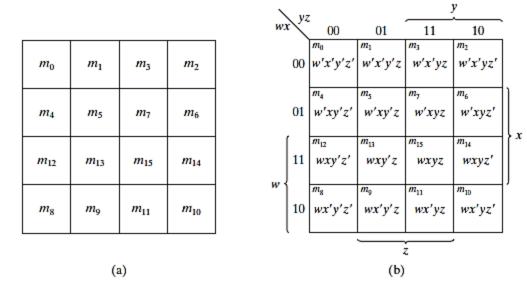

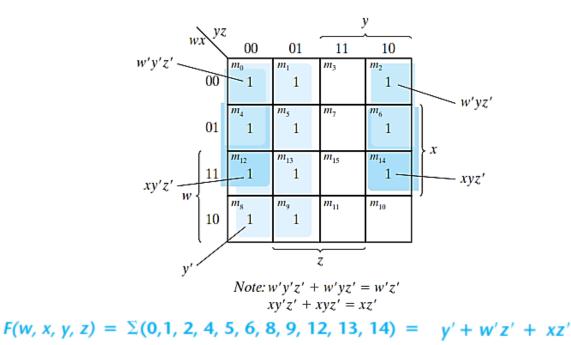

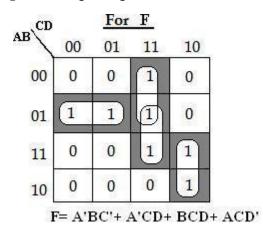

#### K-Maps of 4 Variables:

Simplify the boolean function

$F(w,x,y,z) = \sum (0, 1, 2, 4, 5, 6, 8, 9, 12, 13, 14)$

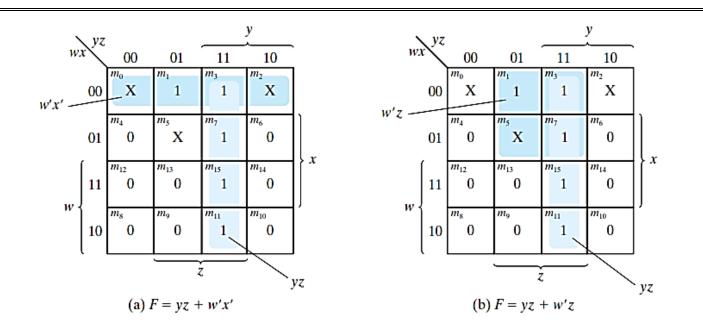

Simplify the Boolean function

\*

$$F(w, x, y, z) = \Sigma(1, 3, 7, 11, 15)$$

which has the don't-care conditions

$$d(w, x, y, z) = \Sigma(0, 2, 5)$$

## Karnaugh Maps - Rules of Simplification

The Karnaugh map uses the following rules for the simplification of expressions by *grouping* together adjacent cells containing *ones*

• Groups may not include any cell containing a zero

• Groups may be horizontal or vertical, but not diagonal.

• Groups must contain 1, 2, 4, 8, or in general  $2^n$  cells. That is if n = 1, a group will contain two 1's since  $2^1 = 2$ . If n = 2, a group will contain four 1's since  $2^2 = 4$ .

• Each group should be as large as possible.

(Note that no Boolean laws broken, but not sufficiently minimal)

• Each cell containing a *one* must be in at least one group.

• There should be as few groups as possible, as long as this does not contradict any of the previous rules.

### Summary:

- 1. No zeros allowed.

- 2. No diagonals.

- 3. Only power of 2 numbers of cells in each group.

- 4. Groups should be as large as possible.

- 5. Everyone must be in at least one group.

- 6. Overlapping allowed.

- 7. Wrap around allowed.

- 8. Fewest numbers of groups possible.

## Don't care combination:

In certain digital systems, some input combinations never occur during the process of normal operation because those input conditions are guaranteed never to occur. Such input combinations are don't care conditions.

### **Completely specified functions:**

If a function is completely specified, it assumes the value 1 for some input combinations and the value 0 for others.

#### **Incompletely specified functions:**

There are functions which assume the value 1 for some combinations and 0 for some other and either 0 or 1 for the remaining combinations. Such a functions are called incompletely specified .

#### **Prime Implicants:**

A prime implicant is a product term obtained by combining the maximum possible number of adjacent squares in the map. If a minterm in a square is covered by only one prime implicant, that prime implicant is said to be essential.

\*\*\*\*\*\*\*\*\*\*\*\*

### Quine-McCluskey (or) Tabulation Method

*Minimization of Logic functions:* Steps:

- $\checkmark$  A set of all prime implicants of the function must be obtained.

- ✓ From the set of prime implicants, a set of essential implicants must be determined by preparing a prime implicant chart.

- ✓ The minterm which are not covered by the essential implicants are taken into consideration and a minimum cover is obtained from the remaining prime implicants.

### Example:

(Nov-06,07,10, May-10,08)

Simplify the boolean function  $F(A,B,C,D) = \sum m (1,3,6,7,8,9,10,12,14,15) + \sum d (11,13)$  using Quine *McClusky method.* (Apr 2017)

## Step:1

| Minterms         | <b>Binary representation</b> | Minterms         | Binary representation |

|------------------|------------------------------|------------------|-----------------------|

| m <sub>1</sub>   | 0001                         | m <sub>1</sub>   | 0001 🗸                |

| m <sub>3</sub>   | 0011                         | m <sub>8</sub>   | 1000 🗸                |

| m <sub>6</sub>   | 0110                         | m <sub>3</sub>   | 0011 🗸                |

| $m_7$            | 0111                         | m <sub>6</sub>   | 0110 🗸                |

| m <sub>8</sub>   | 1000                         | m <sub>9</sub>   | 1001 🗸                |

| m <sub>9</sub>   | 1001                         | m <sub>10</sub>  | 1010 🗸                |

| m <sub>10</sub>  | 1010                         | m <sub>12</sub>  | 1100 🗸                |

| m <sub>12</sub>  | 1100                         | m <sub>7</sub>   | 0111 ✓                |

| m <sub>14</sub>  | 1110                         | m <sub>14</sub>  | 1110 ✓                |

| m <sub>15</sub>  | 1111                         | dm11             | 1011 🗸                |

| dm <sub>11</sub> | 1011                         | dm <sub>13</sub> | 1101 🗸                |

| dm <sub>13</sub> | 1101                         | m <sub>15</sub>  | 1111 ✓                |

## Step:2

| Minterms | Binary representation | Minterms       | Binary representation |

|----------|-----------------------|----------------|-----------------------|

| 1, 3     | 0 0 − 1 🖌             | 1, 3, 9, 11    | -0-1                  |

| 1, 9     | -001 🗸                | 8, 9, 10, 11 🗸 | 10                    |

| 8, 9     | 100- 🗸                | 8, 10, 12, 14  | 1 0                   |

| 8, 10    | 10-0 🗸                |                |                       |

| 8, 12    | 1−00 ✓                | 6, 7, 14, 15 🗸 | -11-                  |

| 3, 7     | 0-11 🗸                |                |                       |

| 3, 11    | -011 🗸                | 12, 13, 14, 15 | 11                    |

| 6, 7     | 011- 🗸                |                |                       |

| 6, 14    | -110 🗸                |                |                       |

| 9, 11    | 10-1 🗸                |                |                       |

| 9, 13    | 1-01 🗸                |                |                       |

| 10, 14   | 1-10 🗸                |                |                       |

| 10, 11   | 101- 🗸                |                |                       |

| 12, 14   | 11-0 🗸                |                |                       |

| 12, 13   | 110- 🗸                |                |                       |

| 7, 15    | -111 🗸                |                |                       |

| 14, 15   | 111- 🗸                |                |                       |

## Step:3

| Prime implicants                 | <b>Binary representation</b> |

|----------------------------------|------------------------------|

| 1, 3, 9, 11 (B D)                | -0-1                         |

| 8, 9, 10, 11, 12, 13, 14, 15 (A) | 1                            |

| 6, 7, 14, 15 (BC)                | -11-                         |

## Step:4

| Prime<br>implicants          | m <sub>1</sub> | m <sub>3</sub> | m <sub>6</sub> | m <sub>7</sub> | m <sub>8</sub> | m <sub>9</sub> | m <sub>10</sub> | m <sub>12</sub> | m <sub>14</sub> | m <sub>15</sub> | dm <sub>11</sub> | dm <sub>13</sub> |

|------------------------------|----------------|----------------|----------------|----------------|----------------|----------------|-----------------|-----------------|-----------------|-----------------|------------------|------------------|

| 1, 3, 9, 11 (BD)             | $\odot$        | $\odot$        |                |                |                | $\odot$        |                 |                 |                 |                 | $\odot$          |                  |

| 8, 9, 10, 11, 12, 13, 14, 15 |                |                |                |                | $\odot$        | $\odot$        | $\odot$         | $\odot$         | $\odot$         | $\odot$         | $\odot$          | $\odot$          |

| 6, 7, 14, 15 (BC)            |                |                | $\odot$        | $\odot$        |                |                |                 |                 | $\odot$         | $\odot$         |                  |                  |

$: \mathbf{F}(\mathbf{A}, \mathbf{B}, \mathbf{C}, \mathbf{D}) = \overline{\mathbf{B}}\mathbf{D} + \mathbf{A} + \mathbf{B}\mathbf{C}$

## Logic gates

Explain about different types of logic gates. (OR) What are Universal gates? Construct any four basic<br/>gates using only NOR gates and using only NAND gates.(May 2011)[NOV - 2019]

✤ A logic gate is an idealized or physical device implementing a Boolean function; that is, it performs a logical operation on one or more logical inputs, and produces a single logical output.

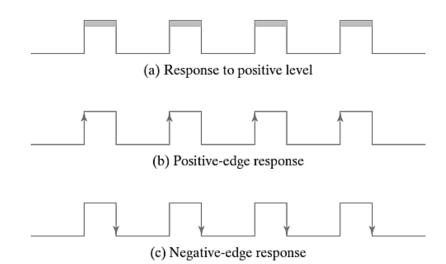

## Positive and Negative Logic

- The binary variables two states, i.e. the logic '0' state or the logic '1' state. These logic states in digital systems such as computers.

- \* These are represented by two different voltage levels or two different current levels.

- If the more positive of the two voltage or current levels represents a logic '1' and the less positive of the two levels represents a logic '0', then the logic system is referred to as a *positive logic system*.

- If the more positive of the two voltage or current levels represents a logic '0' and the less positive of the two levels represents a logic '1', then the logic system is referred to as a *negative logic system*.

## Truth Table

A truth table lists all possible combinations of input binary variables and the corresponding outputs of a logic system.

| Name                               | Graphic<br>symbol | Algebraic<br>function             | Truth<br>table                                                                                                                                        |

|------------------------------------|-------------------|-----------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------|

| AND                                | x<br>y<br>F       | $F = \mathbf{x} \cdot \mathbf{y}$ | x y F<br>0 0 0<br>0 1 0<br>1 0 0<br>1 1 1                                                                                                             |

| OR                                 | x<br>y            | F = x + y                         | x y F<br>0 0 0<br>0 1 1<br>1 0 1<br>1 1 1                                                                                                             |

| Inverter                           | x                 | F = x'                            | x F<br>0 1<br>1 0                                                                                                                                     |

| Buffer                             | x                 | F = x                             | x F<br>0 0<br>1 1                                                                                                                                     |

| NAND                               | x<br>yp           | F = (xy)'                         | x y F<br>0 0 1<br>0 1 1<br>1 0 1<br>1 1 0                                                                                                             |

| NOR                                |                   | F = (x + y)'                      | x y F<br>0 0 1<br>0 1 0<br>1 0 0<br>1 1 0                                                                                                             |

| Exclusive-OR<br>(XOR)              |                   | $F = xy' + x'y$ $= x \oplus y$    | x y F<br>0 0 0<br>0 1 1<br>1 0 1<br>1 1 0                                                                                                             |

| Exclusive-NOR<br>or<br>equivalence | *<br>*            | $F = xy + x'y'$ $= (x \oplus y)'$ | x         y         F           0         0         1           0         1         0           1         0         0           1         1         1 |

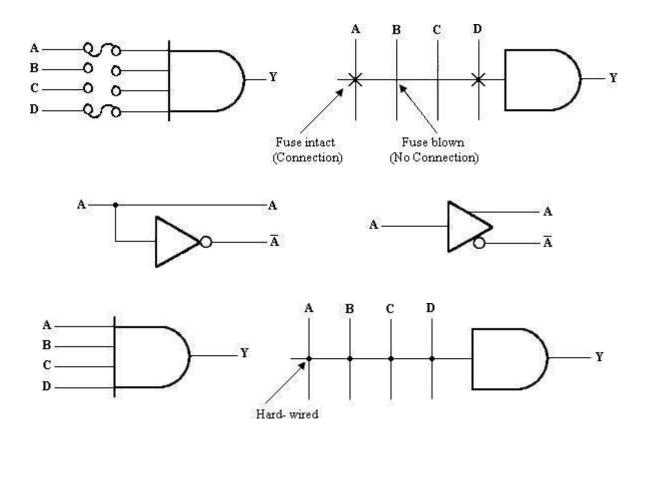

### Universal Gates

- The OR, AND and NOT gates are the three basic logic gates as they together can be used to construct the logic circuit for any given Boolean expression.

- The NOR and NAND gates have the property that they individually can be used to hardwareimplement a logic circuit corresponding to any given Boolean expression.

- That is, it is possible to use either only NAND gates or only NOR gates to implement any Boolean expression. This is so because a combination of NAND gates or a combination of NOR gates can be used to perform functions of any of the basic logic gates. It is for this reason that NAND and NOR gates are universal gates.

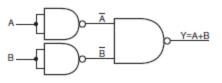

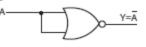

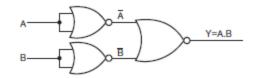

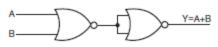

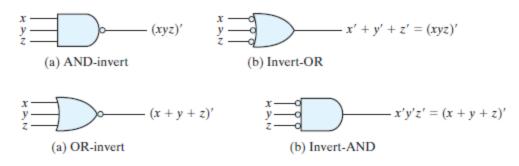

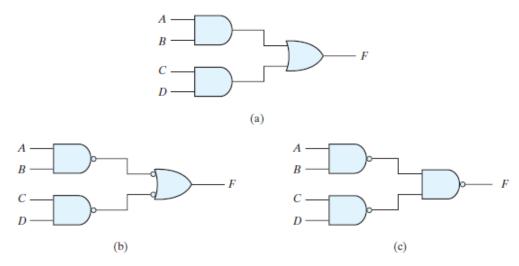

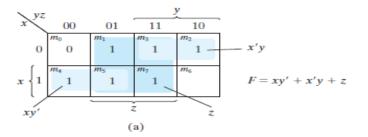

NAND gates and NOR gates are called *universal gates* or *universal building blocks*, as any type of gates or logic functions can be implemented by these gates. Figures Symbolshowshow variouslogic functionscan be realized by NAND gates and Figures Symbolshow therealizationofvariouslogic gatesby NOR gates. A O. A0----F = A' -F = ABBO NOT function: F = A'AND function: F = AB\* Implementation of basic gates using NAND gate: (convert AND gate to NAND gate) Inverter x -AND Logic operations with NAND gates + y' + z' = (xyz)'OR (a) AND-invert (b) Invert-OR Implementation of basic gates using NOR gate: (convert OR gate to NOR gate) Logic operations with NOR gates Inverter x -(x + y + z)'OR (a) OR-invert -x'y'z' = (x+y+z)'AND (b) Invert-AND Implementation of basic gates using NAND gate: **Inverter (NOT gate):** Y=Ā AND gate: Y=A.B R B.ARUNKUMAR, Asst. Prof.,/ECE Page 32

OR gate:

Implementation of basic gates using NOR gate:

Inverter (NOT gate):

AND gate:

OR gate:

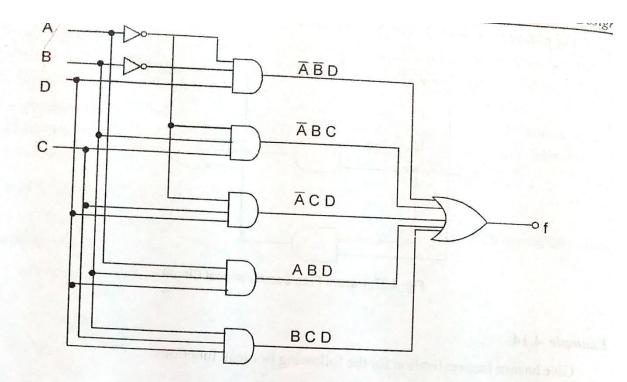

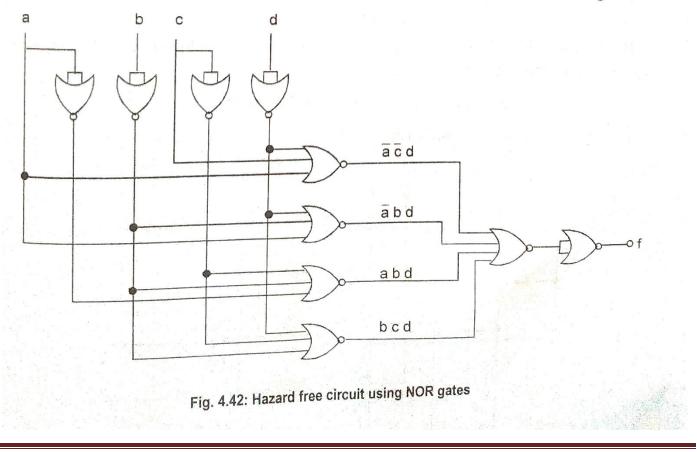

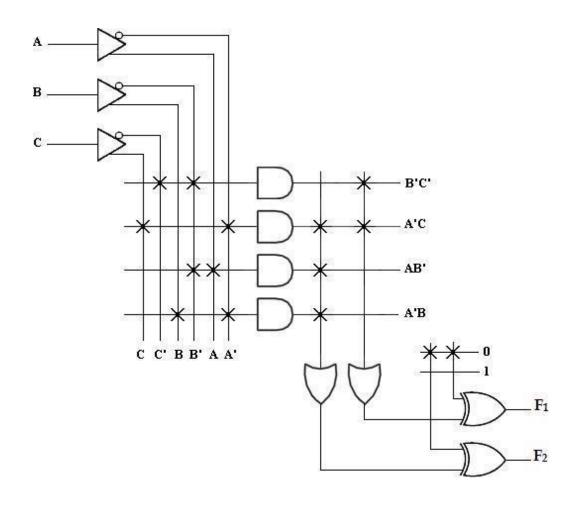

#### NAND-NOR implementations:

- Digital circuits are frequently constructed with NAND or NOR gates rather than with AND and OR gates.

- NAND and NOR gates are easier to fabricate with electronic components and are the basic gates used in all IC digital logic families.

- Because of the prominence of NAND and NOR gates in the design of digital circuits, rules and procedures have been developed for the conversion from Boolean functions given in terms of AND, OR, and NOT into equivalent NAND and NOR logic diagrams.

### Only NAND/NOR gate circuit:

- A convenient way to implement a Boolean function with NAND/NOR gates is to obtain the simplified Boolean function in terms of Boolean operators and then convert the function to NAND/NOR logic.

- The conversion of an algebraic expression from AND, OR, and complement to NAND/NOR can be done by simple circuit manipulation techniques that change AND-OR diagrams to NAND/NOR diagrams.

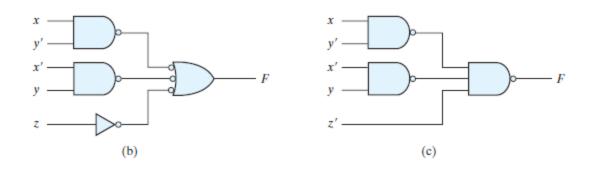

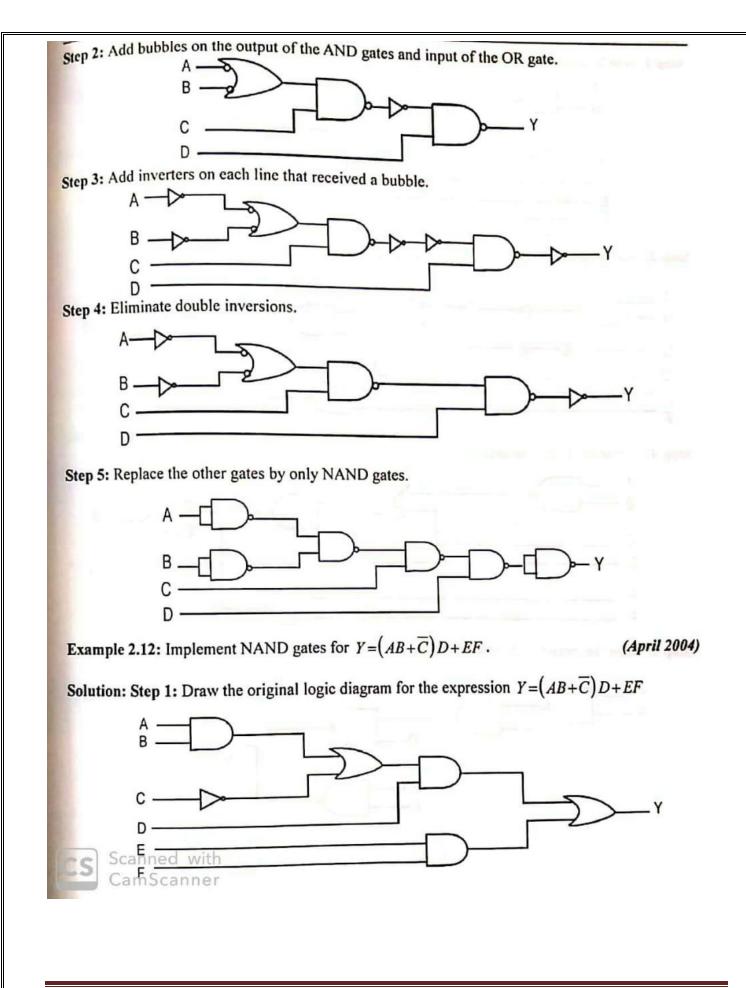

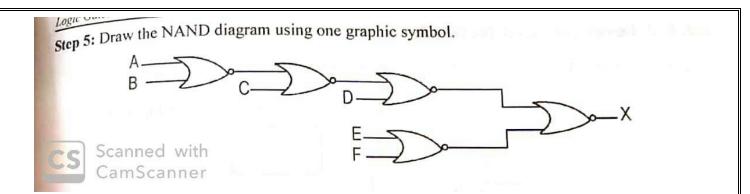

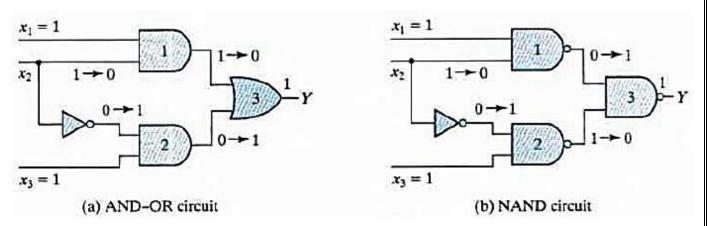

## NAND Implementation Procedure:

- ✓ Draw the AOI logic of given Boolean expression.

- ✓ Add bubble on input of OR gate & output of AND gate.

- ✓ Add an Inverter on each line that received bubbles.

- ✓ Eliminate double inversions

- ✓ Replace all by NAND gates

## Example:

## 1. Implement F = AB + CD using only NAND gate.

2. Implement the following Boolean function with NAND gates: F(x, y, z) = (1, 2, 3, 4, 5, 7) (Apr 2018)

## 3. Implement the function F = (AB' + A'B)(C + D') using only NAND gate.

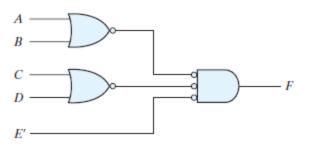

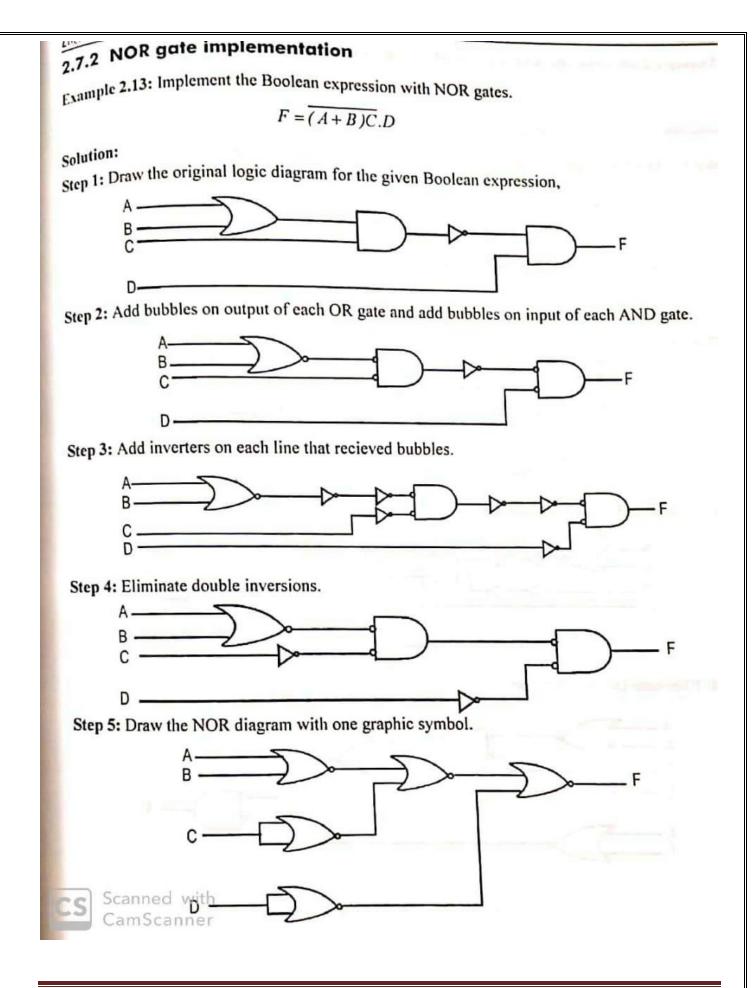

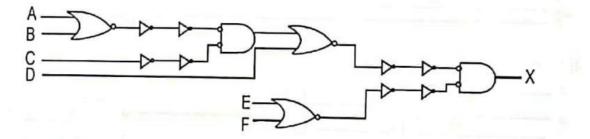

## 2.7.1 NAND gate implementation

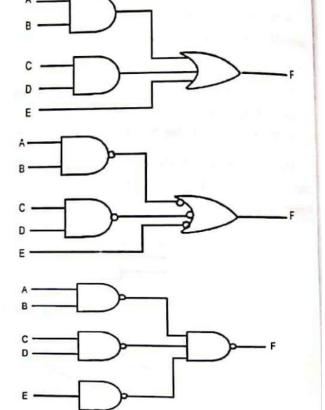

Example 2.10: Implement the Boolean function with NAND gates. F = AB + CD + ESolution:

Step 1: Draw AND-OR circuit.

Step 2: Add bubbles on output of each AND gate and input of OR gate.

Step 3: Replace other gates by NAND gates.

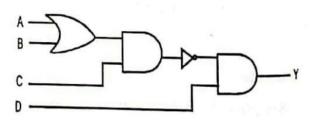

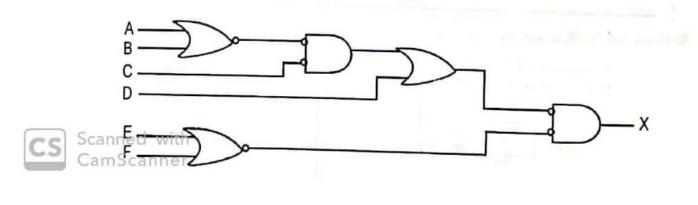

**Example 2.11:** Implement the Boolean expression with NAND gates  $Y = (\overline{(A+B)C})D$

Solution: Step 1: Draw original logic diagram for

$$Y = (\overline{(A+B)C})D$$

Scanned with CamScanner

B.ARUNKUMAR, Asst. Prof.,/ECE

B.ARUNKUMAR, Asst. Prof.,/ECE

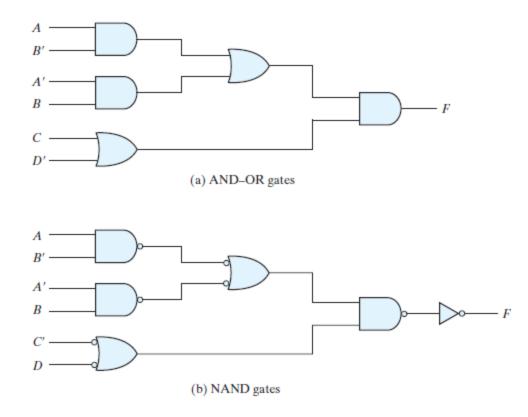

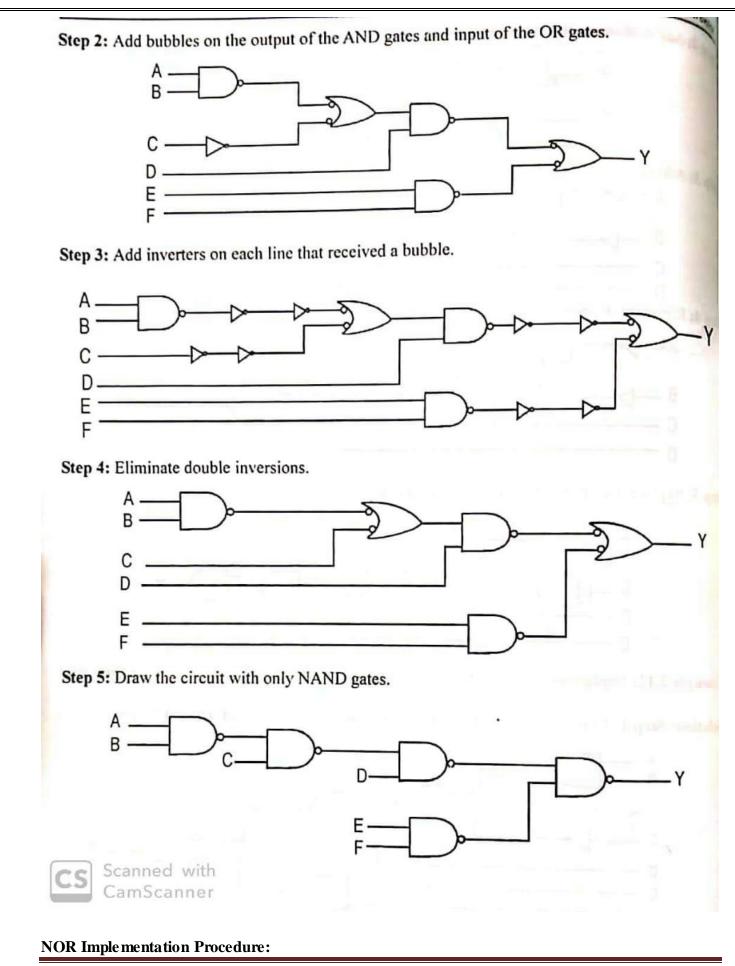

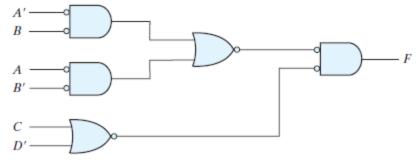

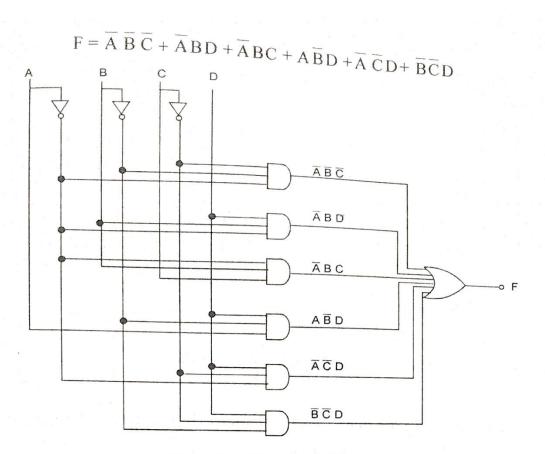

- ✓ Draw the AOI logic of given Boolean expression.

- $\checkmark$  Add bubble on input of AND gate & output of OR gate.

- $\checkmark$  Add an Inverter on each line that received bubbles.

- ✓ Eliminate double inversions

- $\checkmark$  Replace all by NOR gates

#### Example:

1. Implement F = (A + B)(C + D)E using only NOR gate. (Apr 2018)

2. Implement F = (AB' + A'B)(C + D') using only NOR gate.

B.ARUNKUMAR, Asst. Prof.,/ECE

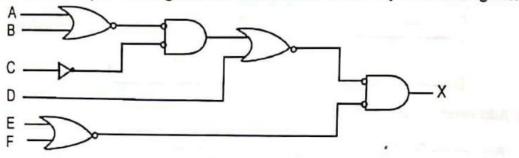

Example 2.14: Draw the multi level NOR circuit for the Boolean expression:

$$X = \left[ (A+B)\overline{C} + D \right] (E+F)$$

# Solution:

Step 1: Draw the original circuit diagram for  $X = \left[ (A+B)\overline{C} + D \right] (E+F)$

Step 2: Add bubbles on the output of OR gates and add bubbles on the input of AND gates.

Step 3: Add inverters on each line that received bubbles.

Step 4: Eliminate Double Versions.

B.ARUNKUMAR, Asst. Prof.,/ECE

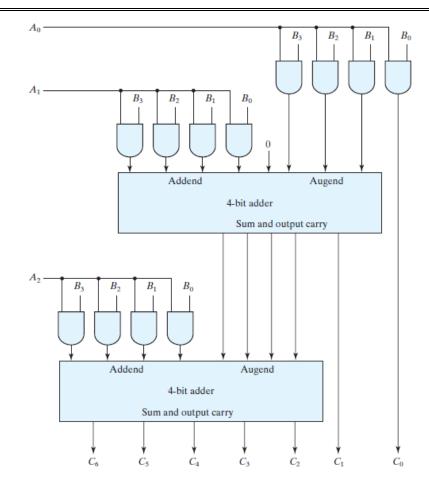

# UNIT II COMBINATIONAL LOGIC

Combinational Circuits – Analysis and Design Procedures - Binary Adder- Subtractor -Decimal Adder -Binary Multiplier - Magnitude Comparator - Decoders – Encoders – Multiplexers - Introduction to HDL – HDL Models of Combinational circuits.

# **COMBINATIONAL CIRCUITS**

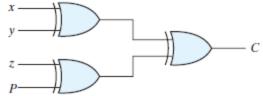

- ✤ A combinational circuit consists of logic gates whose outputs at any time are determined from only the present combination of inputs.

- ✤ A combinational circuit performs an operation that can be specified logically by a set of Boolean functions.

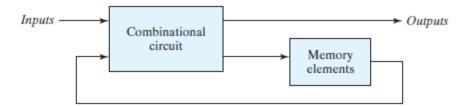

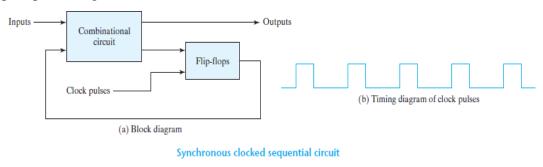

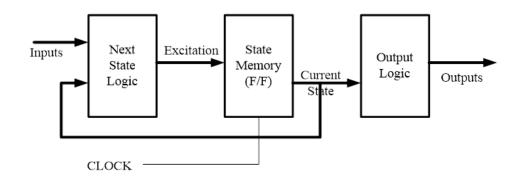

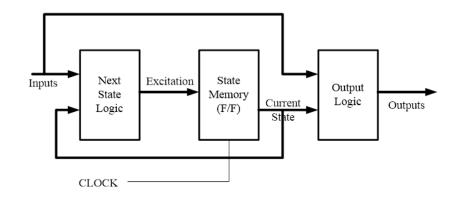

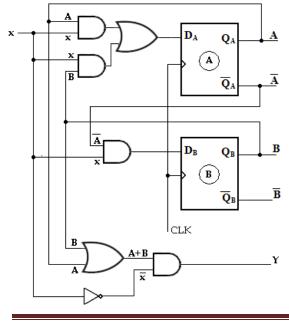

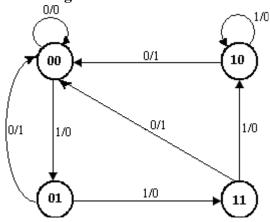

# Sequential circuits:

- Sequential circuits employ storage elements in addition to logic gates. Their outputs are a function of the inputs and the state of the storage elements.

- Because the state of the storage elements is a function of previous inputs, the outputs of a sequential circuit depend not only on present values of inputs, but also on past inputs, and the circuit behavior must be specified by a time sequence of inputs and internal states.

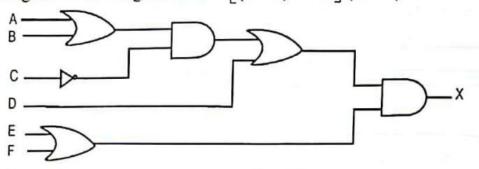

# ANALYSIS PROCEDURE

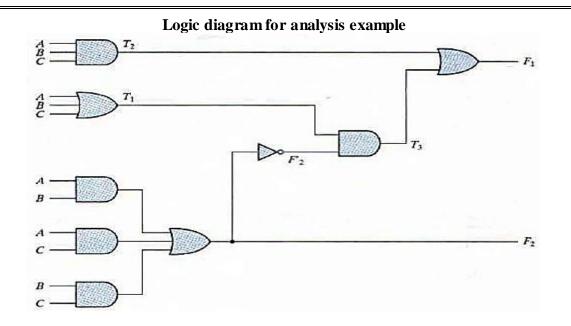

# Explain the analysis procedure. Analyze the combinational circuit the following logic diagram.

(May 2015)

- The analysis of a combinational circuit requires that we determine the function that the circuit implements.

- The analysis can be performed manually by finding the Boolean functions or truth table or by using a computer simulation program.

- The first step in the analysis is to make that the given circuit is combinational or sequential.

- Once the logic diagram is verified to be combinational, one can proceed to obtain the output Boolean functions or the truth table.

- $\checkmark$  To obtain the output Boolean functions from a logic diagram,

- ✓ Label all gate outputs that are a function of input variables with arbitrary symbols or names. Determine the Boolean functions for each gate output.

- ✓ Label the gates that are a function of input variables and previously labeled gates with other arbitrary symbols or names. Find the Boolean functions for these gates.

- $\checkmark$  Repeat the process in step 2 until the outputs of the circuit are obtained.

- ✓ By repeated substitution of previously defined functions, obtain the output Boolean functions in terms of input variables.

The Boolean functions for the above outputs are,

$$F_2 = AB + AC + BC$$

$$T_1 = A + B + C$$

$$T_2 = ABC$$

Next, we consider outputs of gates that are a function of already defined symbols:

$$T_3 = F'_2 T_1$$

$F_1 = T_3 + T_2$

To obtain  $F_1$  as a function of A, B, and C, we form a series of substitutions as follows:

$$F_{1} = T_{3} + T_{2} = F'_{2}T_{1} + ABC = (AB + AC + BC)'(A + B + C) + ABC$$

=  $(A' + B')(A' + C')(B' + C')(A + B + C) + ABC$

=  $(A' + B'C')(AB' + AC' + BC' + B'C) + ABC$

=  $A'BC' + A'B'C + AB'C' + ABC$

Proceed to obtain the truth table for the outputs of those gates which are a function of previously defined values until the columns for all outputs are determined.

#### Truth Table for the Logic Diagram

| A | B | c | F <sub>2</sub> | F'2 | <i>T</i> <sub>1</sub> | T2 | <i>T</i> <sub>3</sub> | F1 |

|---|---|---|----------------|-----|-----------------------|----|-----------------------|----|

| 0 | 0 | 0 | 0              | 91  | 0                     | 0  | 0                     | 0  |

| 0 | o | 1 | o              | 1   | 1                     | 0  | 1                     | 1  |

| 0 | 1 | 0 | 0              | 1   | 1                     | 0  | 1                     | 1  |

| 0 | 1 | 1 | 1              | 0   | 1                     | 0  | 0                     | 0  |

| 1 | 0 | 0 | 0              | 1   | 1                     | 0  | 1                     | 1  |

| 1 | 0 | 1 | 1              | 0   | 1                     | 0  | 0                     | 0  |

| 1 | 1 | 0 | 1 I a          | 0   | 1                     | 0  | 0                     | 0  |

| 1 | 1 | 1 | 1              | 0   | 1                     | 1  | 0                     | 1  |

# DESIGNPROCEDURE

# Explain the procedure involved in designing combinational circuits.

- The design of combinational circuits starts from the specification of the design objective and culminates in a logic circuit diagram or a set of Boolean functions from which the logic diagram can be obtained.

- ✤ The procedure involved involves the following steps,

- ✓ From the specifications of the circuit, determine the required number of inputs and outputs and assign a symbol to each.

- $\checkmark$  Derive the truth table that defines the required relationship between inputs and outputs.

- $\checkmark$  Obtain the simplified Boolean functions for each output as a function of the input variables.

- $\checkmark$  Draw the logic diagram and verify the correctness of the design.

#### \*\*\*\*\*\*\*

# CIRCUITS FOR ARITHMETIC OPERATIONS

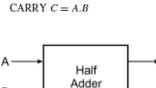

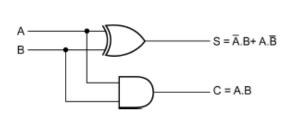

# Half adder:

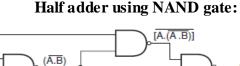

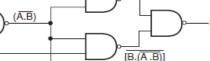

Construct a half adder with necessary diagrams.

(Nov-06, May- 07)

- ✤ A half-adder is an arithmetic circuit block that can be used to add two bits and produce two outputs SUM and CARRY.

- The Boolean expressions for the SUM and CARRY outputs are given by the equations

SUM  $S = A.\overline{B} + \overline{A}.B$

A

В

# Truth Table:

| А | В | s | С |

|---|---|---|---|

| 0 | 0 | 0 | 0 |

| 0 | 1 | 1 | 0 |

| 1 | 0 | 1 | 0 |

| 1 | 1 | 0 | 1 |

# Logic Diagram:

۰s

C

\*\*\*\*\*

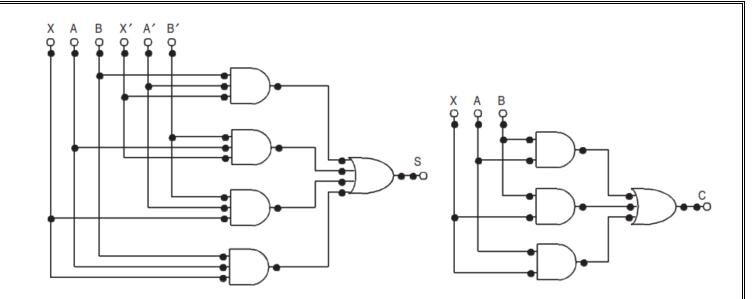

#### Full adder:

Design a full adder using NAND and NOR gates respectively.

- A Full-adder is an arithmetic circuit block that can be used to add three bits and produce two outputs SUM and CARRY.

- ✤ The Boolean expressions for the SUM and CARRY outputs are given by the equations

$$\begin{split} S &= \overline{A}.\overline{B}.C_{\text{in}} + \overline{A}.B.\overline{C}_{\text{in}} + A.\overline{B}.\overline{C}_{\text{in}} + A.B.C_{\text{in}} \\ C_{\text{out}} &= B.C_{\text{in}} + A.B + A.C_{\text{in}} \end{split}$$

#### Truth table:

|   | Input variables | Outputs |   |   |

|---|-----------------|---------|---|---|

| X | Α               | В       | S | С |

| 0 | 0               | 0       | 0 | 0 |

| 0 | 0               | 1       | 1 | 0 |

| 0 | 1               | 0       | 1 | 0 |

| 0 | 1               | 1       | 0 | 1 |

| 1 | 0               | 0       | 1 | 0 |

| 1 | 0               | 1       | 0 | 1 |

| 1 | 1               | 0       | 0 | 1 |

| 1 | 1               | 1       | 1 | 1 |

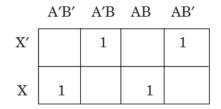

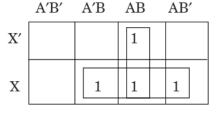

#### Karnaugh map:

K-Map for Sum

K-Map for Carry

✤ The simplified Boolean expressions of the outputs are

S = X'A'B + X'AB' + XA'B' + XABC = AB + BX + AX

Logic diagram:

✤ The Boolean expressions of S and C are modified as follows

$$S = X'A'B + X'AB' + XA'B' + XAB$$

= X' (A'B + AB') + X (A'B' + AB)

= X' (A  $\oplus$  B) + X (A  $\oplus$  B)'

= X  $\oplus$  A  $\oplus$  B

C = AB + BX + AX = AB + X (A + B)

= AB + X (AB + AB' + AB + A'B)

= AB + X (AB + AB' + A'B)

= AB + XAB + X (AB' + A'B)

= AB + X (A  $\oplus$  B)

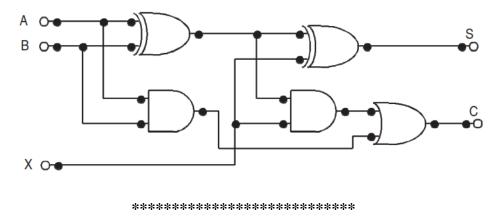

# Full adder using Two half adder:

✤ Logic diagram according to the modified expression is shown Figure.

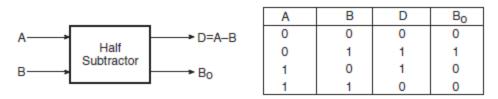

# Half subtractor: Design a half subtractor circuit.

(Nov-2009)

- ✤ A half-subtractor is a combinational circuit that can be used to subtract one binary digit from another to produce a DIFFERENCE output and a BORROW output.

- The BORROW output here specifies whether a '1' has been borrowed to perform the subtraction. The Boolean expression for difference and borrow is:

$$D = \overline{A}.B + A.\overline{B}$$

$$B_0 = \overline{A}.B$$

#### Logic diagram:

\*\*\*\*\*

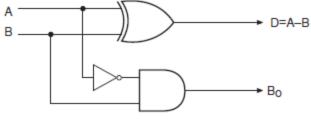

# Full subtractor:

# Design a full subtractor.

#### (Nov-2009,07)

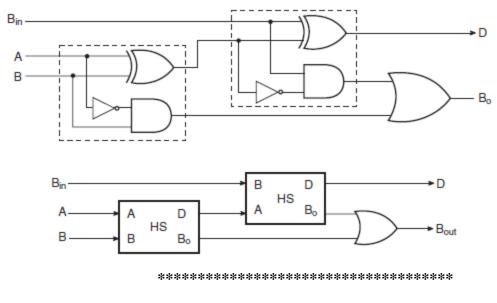

- A full subtractor performs subtraction operation on two bits, a minuend and a subtrahend, and also takes into consideration whether a '1' has already been borrowed by the previous adjacent lower minuend bit or not.

- As a result, there are three bits to be handled at the input of a full subtractor, namely the two bits to be subtracted and a borrow bit designated as Bin.

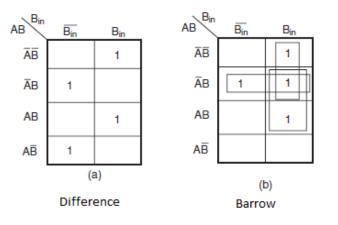

- There are two outputs, namely the DIFFERENCE output D and the BORROW output Bo. The BORROW output bit tells whether the minuend bit needs to borrow a '1' from the next possible higher minuend bit. The Boolean expression for difference and barrow is:

$D = \overline{A}.\overline{B}.B_{in} + \overline{A}.B.\overline{B}_{in} + A.\overline{B}.\overline{B}_{in} + A.B.B_{in}$  $B_0 = \overline{A}.B + \overline{A}.B_{in} + B.B_{in}$

|             | Minuend<br>(A) | Subtrahend<br>(B) | Borrow<br>In (Bin) | Difference<br>(D) | Borrow<br>Out (B <sub>0</sub> ) |

|-------------|----------------|-------------------|--------------------|-------------------|---------------------------------|

|             | 0              | 0                 | 0                  | 0                 | 0                               |

|             | 0              | 0                 | 1                  | 1                 | 1                               |

| A → D       | 0              | 1                 | 0                  | 1                 | 1                               |

| B Full      | 0              | 1                 | 1                  | 0                 | 1                               |

| Bin Bin Bin | 1              | 0                 | 0                  | 1                 | 0                               |

|             | 1              | 0                 | 1                  | 0                 | 0                               |

|             | 1              | 1                 | 0                  | 0                 | 0                               |

|             | 1              | 1                 | 1                  | 1                 | 1                               |

K-Map:

Full subtractor using two half subtractor:

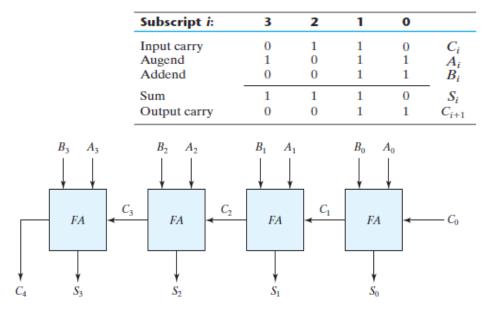

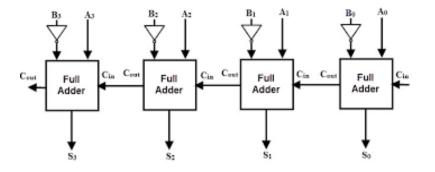

#### Parallel Binary Adder: (Ripple Carry Adder):

# Explain about four bit adder. (or) Design of 4 bit binary adder – subtractor circuit. (Apr – 2019)

- A binary adder is a digital circuit that produces the arithmetic sum of two binary numbers. It can be constructed with full adders connected in cascade, with the output carry from each full adder connected to the input carry of the next full adder in the chain.

- ☆ Addition of n-bit numbers requires a chain of n- full adders or a chain of one-half adder and n-1 full adders. In the former case, the input carry to the least significant position is fixed at 0.

- Figure shows the interconnection of four full-adder (FA) circuits to provide a four-bit binary ripple carry adder.

- The carries are connected in a chain through the full adders. The input carry to the adder is C0, and it ripples through the full adders to the output carry C4. The S outputs generate the required sum bits.

**Example:** Consider the two binary numbers A = 1011 and B = 0011. Their sum S = 1110 is formed with the four-bit adder as follows:

- ✓ The carry output of lower order stage is connected to the carry input of the next higher order stage. Hence this type of adder is called ripple carry adder.

- ✓ In a 4-bit binary adder, where each full adder has a propagation delay of tp ns, the output in the fourth stage will be generated only after 4tp ns.

- $\checkmark$  The magnitude of such delay is prohibitive for high speed computers.

- ✓ One method of speeding up this process is look-ahead carry addition which eliminates ripple carry delay.

#### \*\*\*\*\*

#### Complement of a number:

#### 1's complement:

The 1's complement of a binary number is formed by changing 1 to 0 and 0 to 1.

#### Example:

- 1. The 1's complement of 1011000 is 0100111.

- 2. The 1's complement of 0101101 is 1010010.

#### 2's complement:

The 2's complement of a binary number is formed by adding 1 with 1's complement of a binary number.

# Example:

- 1. The 2's complement of 1101100 is 0010100

- 2. The 2's complement of 0110111 is 1001001

#### Subtraction using 2's complement addition:

- $\checkmark$  The subtraction of unsigned binary number can be done by means of complements.

- $\checkmark$  Subtraction of A-B can be done by taking 2's complement of B and adding it to A.

- $\checkmark$  Check the resulting number. If carry present, the number is positive and remove the carry.

- ✓ If no carry present, the resulting number is negative, take the 2's complement of result and put negative sign.

#### Example:

Given the two binary numbers X = 1010100 and Y = 1000011, perform the subtraction (a) X - Y and (b) Y - X by using 2's complements.

#### Solution:

(a) X = 10101002's complement of Y = + 0111101Sum= 10010001 Discard end carry. *Answer*: X - Y = 0010001(b) Y = 10000112's complement of X = + 0101100Sum= 1101111 There is no end carry. Therefore, the answer is Y - X = -(2's complement of 1101111) =-0010001.

#### \*\*\*\*\*

#### Parallel Binary Subtractor:

✓ The subtraction of unsigned binary numbers can be done most conveniently by means of complements. The subtraction A - B can be done by taking the 2's complement of B and adding it to A. The 2's complement can be obtained by taking the 1's complement and adding 1 to the least significant pair ofbits. The 1's complement can be implemented with inverters, and a 1 can be added to the sum through the input carry.

- ✓ The circuit for subtracting A B consists of an adder with inverters placed between each data input B and the corresponding input of the full adder. The input carry C in must be equal to 1 when subtraction is performed. The operation thus performed becomes A, plus the 1's complement of B, plus 1. This is equal to A plus the 2's complement of B.

- ✓ For unsigned numbers, that gives *A*-*B* if *A*>=*B* or the 2's complement of *B* Aif *A* <*B*. For signed numbers, the result is *A B*, provided that there is no overflow.

\*\*\*\*\*

# Fast adder (or) Carry Look Ahead adder:

Design a carry look ahead adder circuit.

(Nov-2010)

- The carry look ahead adder is based on the principle of looking at the lower order bits of the augend and addend to see if a higher order carry is to be generated.

- ✤ It uses two functions carry generate and carry propagate.

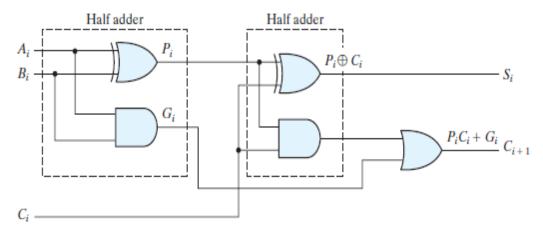

Consider the circuit of the full adder shown in Fig. If we define two new binaryvariables

$$P_i = A_i \oplus B_i$$

$$G_i = A_i B_i$$

the output sum and carry can respectively be expressed as

$$S_i = P_i \oplus C_i$$

$$C_{i+1} = G_i + P_i C_i$$

Gi is called a carry generate, and it produces a carry of 1 when both Ai and Bi are 1, regardless of the input carry Ci. Pi is called a carry propagate, because it determines whether a carry into stage i will propagate into stage i + 1 (i.e., whether an assertion of Ci will propagate to an assertion of Ci+1).

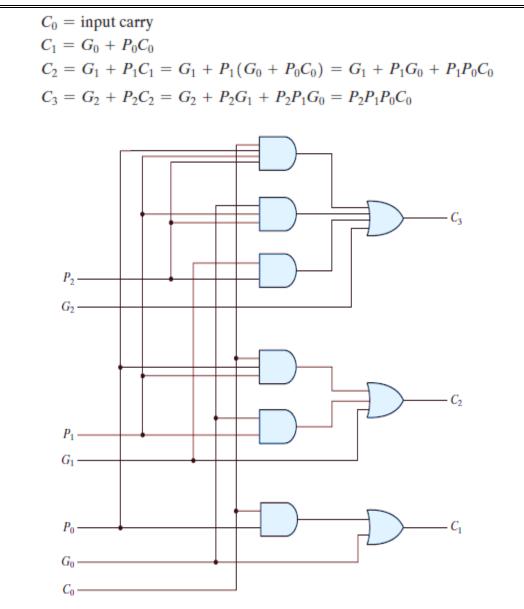

We now write the Boolean functions for the carry outputs of each stage and substitute the value of each Ci from the previous equations:

Logic diagram of carry lookahead generator

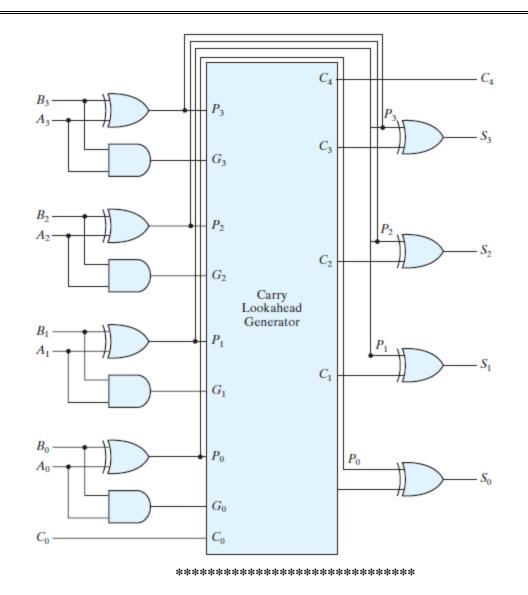

- \* The construction of a four-bit adder with a carry lookahead scheme is shown in Fig.

- Each sum output requires two exclusive-OR gates.

- The output of the first exclusive-OR gate generates the Pi variable, and the AND gate generates the Gi variable.

- The carries are propagated through the carry look ahead generator and applied as inputs to the second exclusive-OR gate.

- ✤ All output carries are generated after a delay through two levels of gates.

- Thus, outputs S1 through S3 have equal propagation delay times. The two-level circuit for the output carry C4 is not shown. This circuit can easily be derived by the equation-substitution method.

# 4 bit-Parallel adder/subtractor:

# Explain about binary parallel / adder subtractor. [NOV - 2019]

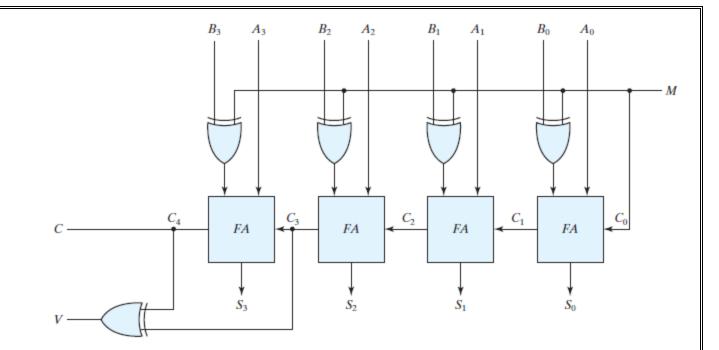

- The addition and subtraction operations can be combined into one circuit with one common binary adder by including an exclusive-OR gate with each full adder. A four-bit adder–subtractor circuit is shown in Fig.

- ★ The mode input *M* controls the operation. When M = 0, the circuit is an adder, and when M = 1, the circuit becomes a subtractor.

- It performs the operations of both addition and subtraction.

- It has two 4bit inputs  $A_3A_2A_1A_0$  and  $B_3B_2B_1B_0$ .

- ✤ The mode input M controls the operation when M=0 the circuit is an adder and when M=1 the circuits become subtractor.

- $\clubsuit$  Each exclusive-OR gate receives input *M* and one of the inputs of *B*.

- ♦ When M = 0, we have B xor0 = B. The full adders receive the value of B, the input carry is 0, and the circuit performs A plus B. This results in sum S<sub>3</sub>S<sub>2</sub>S<sub>1</sub>S<sub>0</sub> and carry C<sub>4</sub>.

- ♦ When M = 1, we have B xor 1 = B' and  $C_0 = 1$ . The B inputs are all complemented and a 1 is added through the input carry thus producing 2's complement of B.

- ☆ Now the data A<sub>3</sub>A<sub>2</sub>A<sub>1</sub>A<sub>0</sub>will be added with 2's complement of B<sub>3</sub>B<sub>2</sub>B<sub>1</sub>B<sub>0</sub>to produce the sum i.e., A-B if A≥B or the 2's complement of B-A if A<B.</p>

#### \*\*\*\*\*

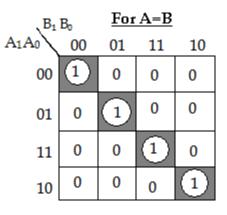

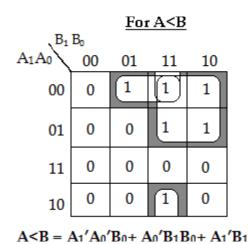

#### **Comparators**

Design a 2 bit magnitude comparator.

(May 2006)

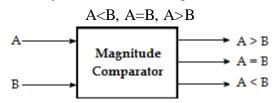

It is a combinational circuit that compares two numbers and determines their relative magnitude. The output of comparator is usually 3 binary variables indicating:

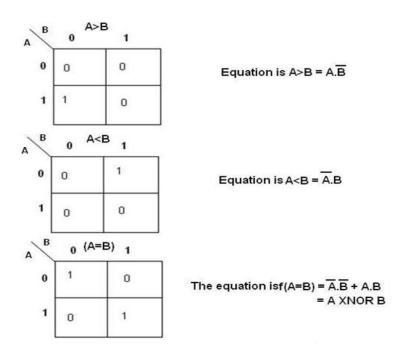

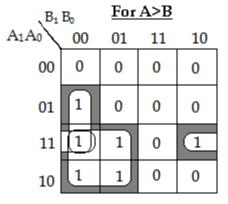

**1-bitcomparator:** Let's begin with 1bit comparator and from the name we can easily make out that this circuit would be used to compare 1bit binary numbers.

| Α | В | A>B | A=B | A <b< th=""></b<> |

|---|---|-----|-----|-------------------|

| 0 | 0 | 0   | 1   | 0                 |

| 1 | 0 | 1   | 0   | 0                 |

| 0 | 1 | 0   | 0   | 1                 |

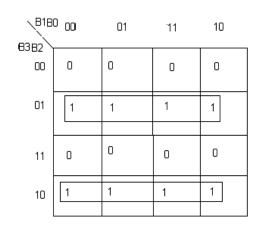

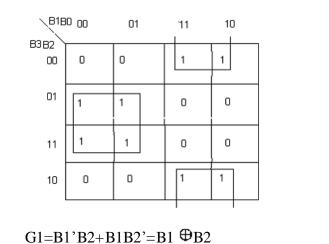

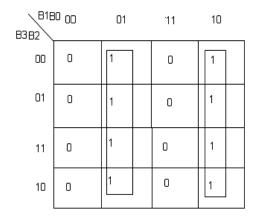

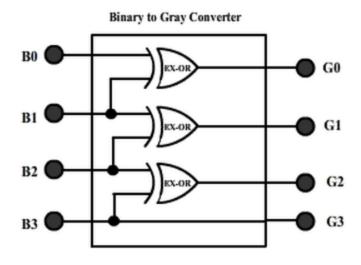

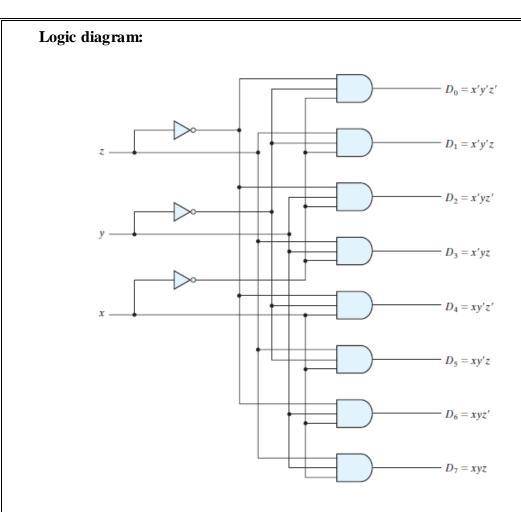

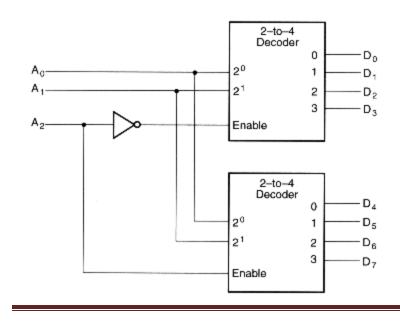

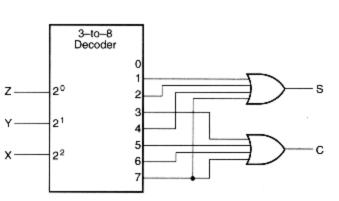

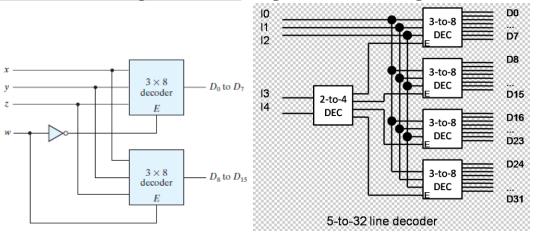

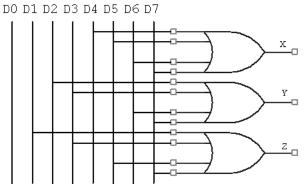

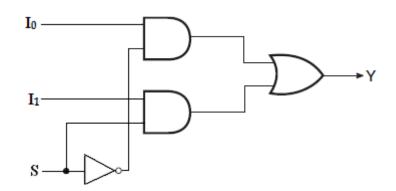

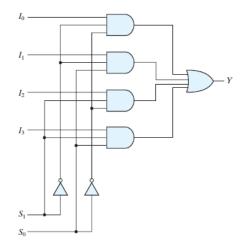

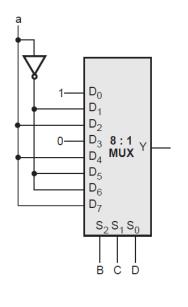

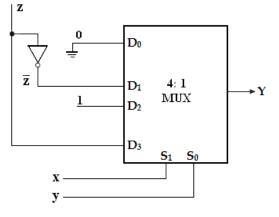

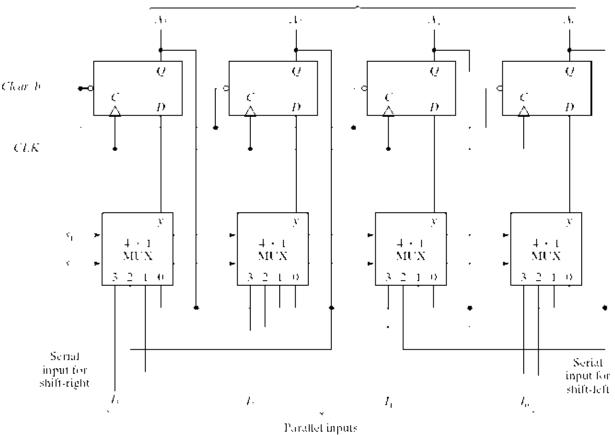

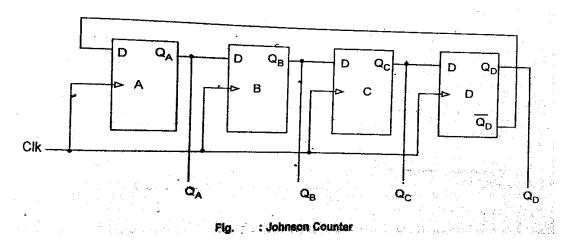

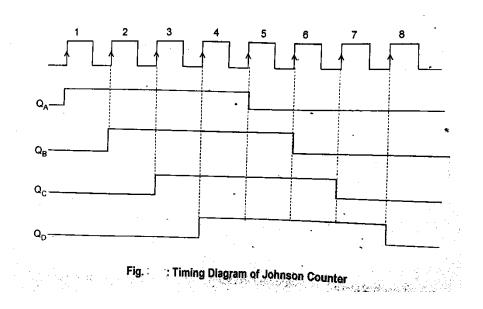

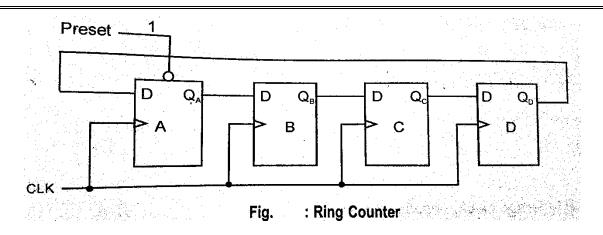

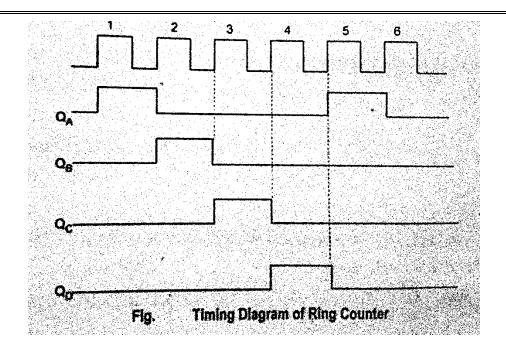

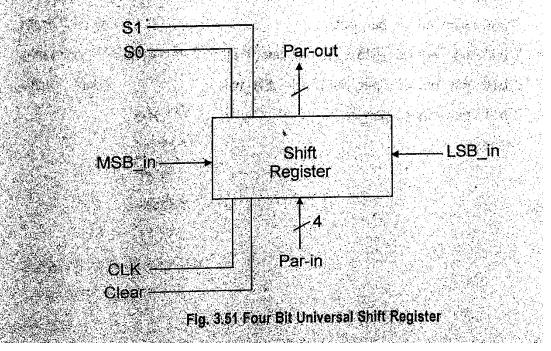

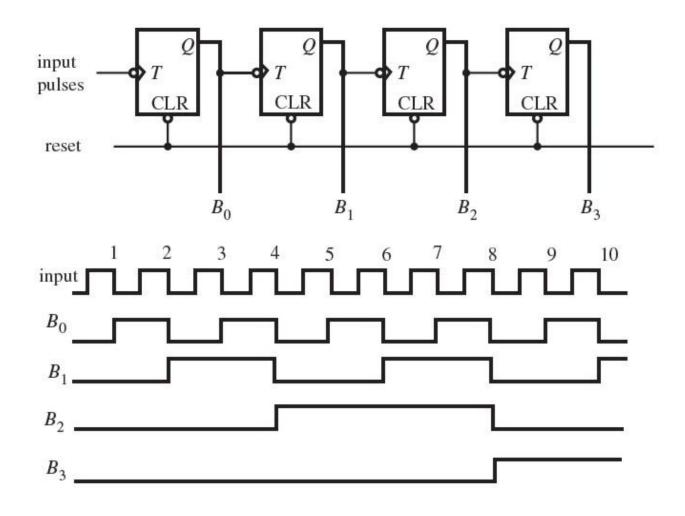

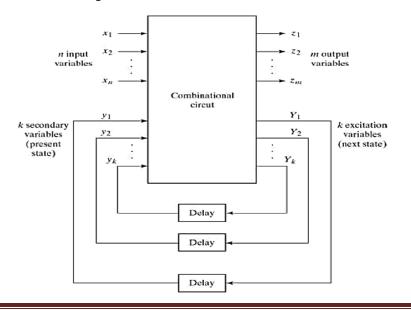

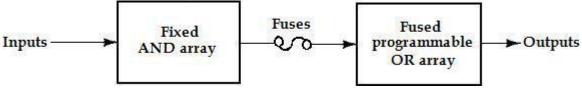

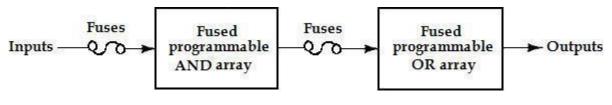

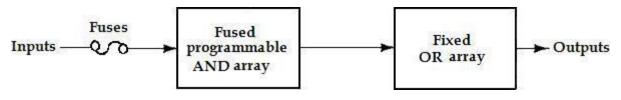

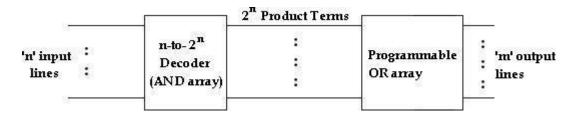

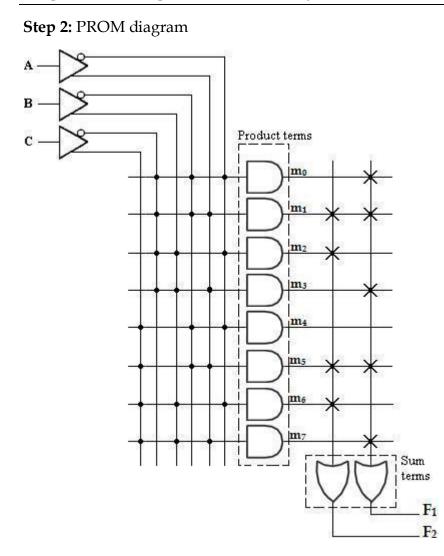

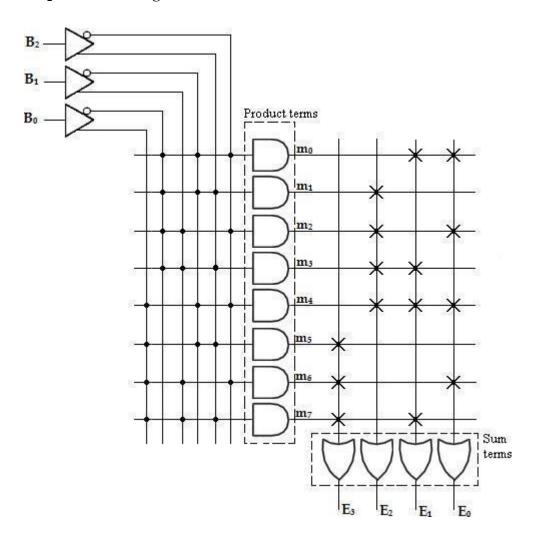

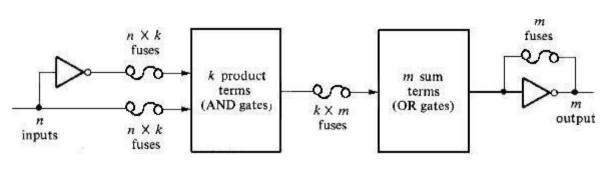

| 1 | 1 | 0   | 1   | 0                 |